VP536E View Datasheet(PDF) - Zarlink Semiconductor Inc

Part Name

Description

View to exact match

VP536E Datasheet PDF : 14 Pages

| |||

VP536E

Pin Descriptions

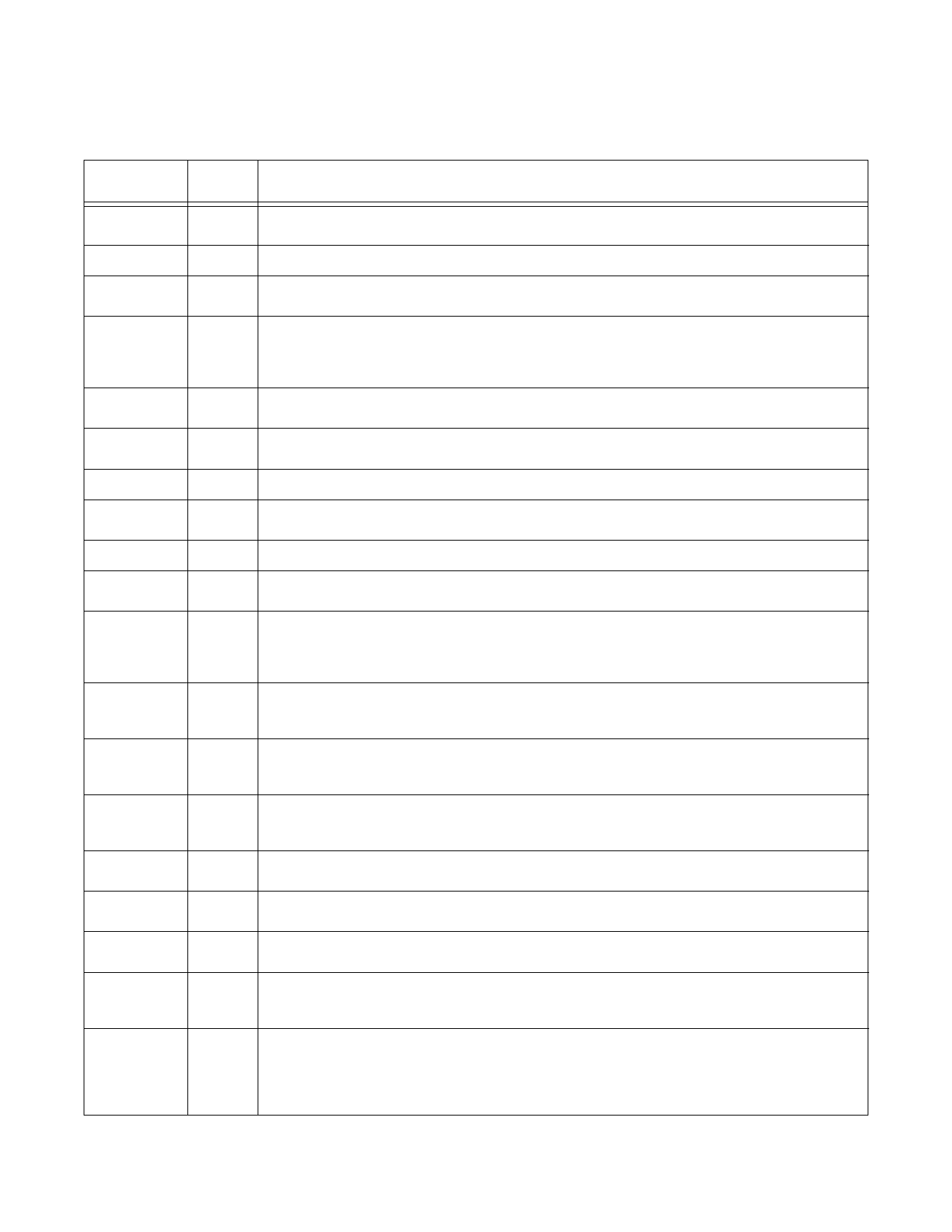

Table 4: Pin Descriptions

Pin Name Pin No.

Description

B0-B7

G0-G7

R0-R6, R7

CLK25I

CLK12I

CLK25O

CLK12O

HS

VS

RESET

CTRLA1

CTRLA2

CTRLA3

CTRLB1

CTRLB2

TCSPK

TSURST

VREF

LUMA-

COMP

CHROMA-

COMP

LUMAOUT

COMPOUTB

CHROMAOUT

LUMAGAIN

2-9

8 Bit Blue data inputs. B0 is the least significant bit, corresponding to Pin 2. These pins are internally pulled

low.

17-24 8 Bit Green data inputs. G0 is the least significant bit. These pins are internally pulled low.

62-68, 1

57

60

61

8 Bit Red data inputs. R7 is the most significant bit corresponding to Pin 1. These pins are internally pulled

low.

2X pixel rate clock input. The VP536E requires a clock whose frequency is twice the input pixel data rate; i.e.,

25.0489484MHz. for the NTSC mode of operation; 29.500000MHz. for the PAL mode of operation.This clock

must be derived from a crystal controlled oscillator in order to avoid chroma frequency, modulation and timing

errors.

Pixel rate clock input. The frequency of this clock must be exactly half that of the CLK25I clock. The rising

edges of these two clocks must be synchronous.

2X pixel rate clock output. The CLK25I clock is output on this pin. Note that this output clock signal is inverted

with respect to the CLK25I clock.

51

Pixel rate clock output. The CLK12I clock is output on this pin.

14

Horizontal sync pulse output. This is an active low signal output, i.e. the presence of a sync pulse is denoted

by the signal being low.

13

Vertical sync pulse output. This is an active low signal output.

16

VP536E master reset. This is an active low input signal and must be asserted for a minimum of 2 CLK12I

clock periods in order to reset the VP536E.

59

58

54

Input data format and dithering control. Control codes on these three input pins determine the format of the

input data as described in Input Pixel Data Format on Page 2. CTRLA1 is internally pulled high, while

CTRLA2 and CTRLA3 are internally pulled low; therefore if left open, the default input data format is pre-

gamma corrected RGB with dithering as described on Page 2.

52

53

Video standard control. Control codes on these two input pins determine the video display mode as

described in Table 1 on Page 2. These pins are internally pulled low, therefore if left open, the default video

display mode is NTSC.

Enable/Disable extended video bandwidth. Taking this pin high limits the bandwidth of the video signal as

49

described in Extendable S-Video Bandwidth on Page 3. This pin is internally pulled low, therefore if left open,

extended bandwidth is enabled.

Synchronous reset of video timing. An active high pulse on this pin resets the video timing generator without

50

affecting the data path. On the rising edge of CLK12I following TSURST going low, Field 1, line 1 is initiated.

This pin is internally pulled low.

28

Voltage reference output. This output is nominally 1.0V and should be decoupled with a 1.0µF capacitor to

GND.

30

Luma DAC compensation. A 0.1µF ceramic capacitor must be connected between this pin and it’s

neighboring VAA pin (pin 31).

38

Chroma DAC compensation. A 0.1µF ceramic capacitor must be connected between this pin and it’s

neighboring VAA pin (pin 37).

32

34

36

Luminance, inverted composite and chrominance video signal outputs. These outputs are high impedance

current source outputs. A DC path to GND must exist from each of these pins.

Luminance full scale current control. A resistor connected between this pin and GND sets the magnitude of

the luminance video output current. An internal loop amplifier controls a reference current flowing through

29

this resistor so that the voltage across it is equal to the Vref voltage. This reference current has a weighting

equal to 16 LSB’s. Note that the IRE relationships shown in Fig. 3 are maintained, regardless of the output

full scale current.

7