EDS1232AATA-75MI View Datasheet(PDF) - Elpida Memory, Inc

Part Name

Description

View to exact match

EDS1232AATA-75MI Datasheet PDF : 53 Pages

| |||

EDS1232AATA-MI

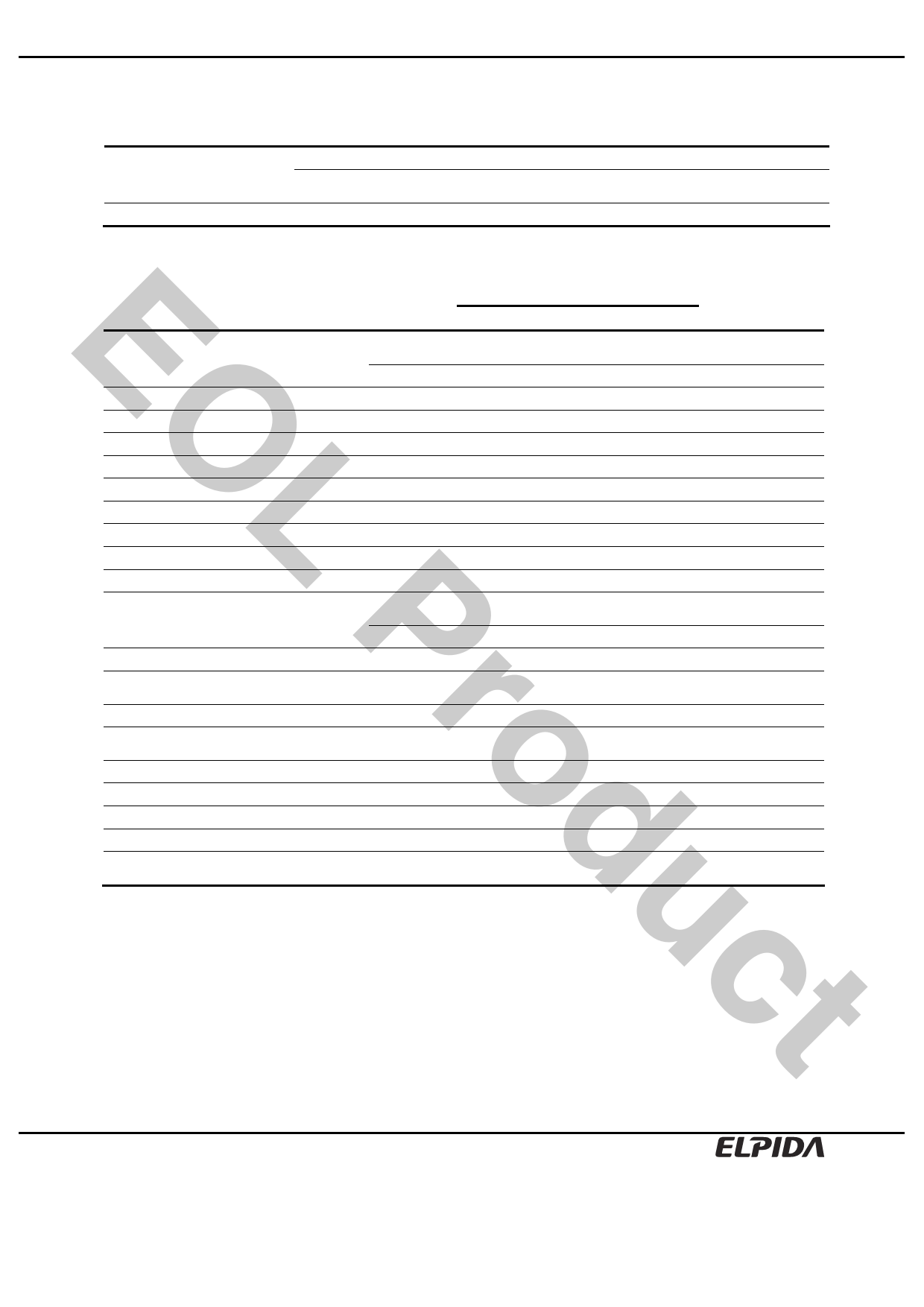

Pin Capacitance (TA = 25°C, f = 1MHz)

Parameter

Symbol Pins

min.

typ.

max.

Unit Notes

Input capacitance

CI1

Address

2.5

—

4.0

pF

CI2

CLK, CKE, /CS, /RAS,

/CAS, /WE, DQM

2.5

—

4.0

pF

Data input/output capacitance CI/O

DQ

4.0

—

6.5

pF

AC Characteristics (TA = –40 to +85°C, VDD, VDDQ = 3.3V±0.3V, VSS, VSSQ = 0V)

Parameter

ESystem clock cycle time

(CL = 2)

(CL = 3)

CLK high pulse width

OCLK low pulse width

Access time from CLK

Data-out hold time

L CLK to Data-out low impedance

-75

Symbol

min.

tCK

10

tCK

7.5

tCH

2.5

tCL

2.5

tAC

—

tOH

2

tLZ

0

max.

—

—

—

—

5.4

—

—

Unit

Notes

ns

ns

ns

ns

ns

ns

ns

CLK to Data-out high impedance

tHZ

2

5.4

ns

Input setup time

tSI

1.5

—

ns

Input hold time

tHI

0.8

—

ns

CKE setup time (Power down exit)

tCKSP

1.5

—

ns

ACT to REF/ACT command period

P (operation)

tRC

67.5

⎯

ns

(refresh)

tRC

67.5

⎯

ns

Active to Precharge command period

tRAS

45

120000

ns

Active command to column command (same

bank)

tRCD

20

⎯

ns

r Precharge to active command period

tRP

20

⎯

ns

Write recovery or data-in to precharge

o lead time

tDPL

15

⎯

ns

Last data into active latency

tDAL

2CLK + 20ns

⎯

Active (a) to Active (b) command period

tRRD

15

⎯

ns

d Mode register set cycle time

tRSC

2

⎯

CLK

Transition time (rise and fall)

tT

0.5

30

ns

Refresh period

uct (4096 refresh cycles)

tREF

—

64

ms

Data Sheet E0340E30 (Ver. 3.0)

6