SST89C54-33-I-PJ View Datasheet(PDF) - Silicon Storage Technology

Part Name

Description

View to exact match

SST89C54-33-I-PJ Datasheet PDF : 50 Pages

| |||

FlashFlex51 MCU

SST89C54 / SST89C58

Preliminary Specifications

When the chip is in the External Host Mode, Port 0 pins The insertion of an “arming” command prior to entering

are assigned to be the parallel data input and output pins. the External Host Mode by utilizing the “READ-ID” op-

Port 1 pins are assigned to be the non-multiplexed low

order address bus signals for the internal flash memory

eration provides additional protection for inadvertent

writes to the internal flash memory caused by a noisy or

1

(A7-A0). The first six bits of Port 2 pins (P2[5:0]) are unstable system environment during power-up or brown-

assigned to be the non-multiplexed upper order address

bus signals for the internal flash memory (A13-A8) along

out conditions.

The External Host Mode uses twelve (12) hardware

2

with two of the Port 3 pins (P3[5] as A15 and P3[4] as

commands, which are decoded from the control signal

A14). Two upper order Port 2 pins (P2[7] and P2[6]) and

two upper order Port 3 pins (P3[7] and P3[6]) along with

pins, to facilitate the internal flash memory erase, pro-

gram and verify processes. The External Host Mode is

3

RST, PSEN#, PROG#/ALE, EA# pins are assigned as

enabled on the falling edge of PSEN#. The External Host

the control signal pins. The Port 3 pin (P3[3]) is assigned

to be the ready/busy status signal, which can be used for

Mode Commands are enabled on the falling edge of ALE/

PROG#. The list in Table 4 outlines all the commands

4

handshaking with the external host during a flash

and the respective control signal assignment.

memory programming operation. The flash memory

programming operation (Erase, Program, Verify, etc.) is

5

internally self-timed.

6

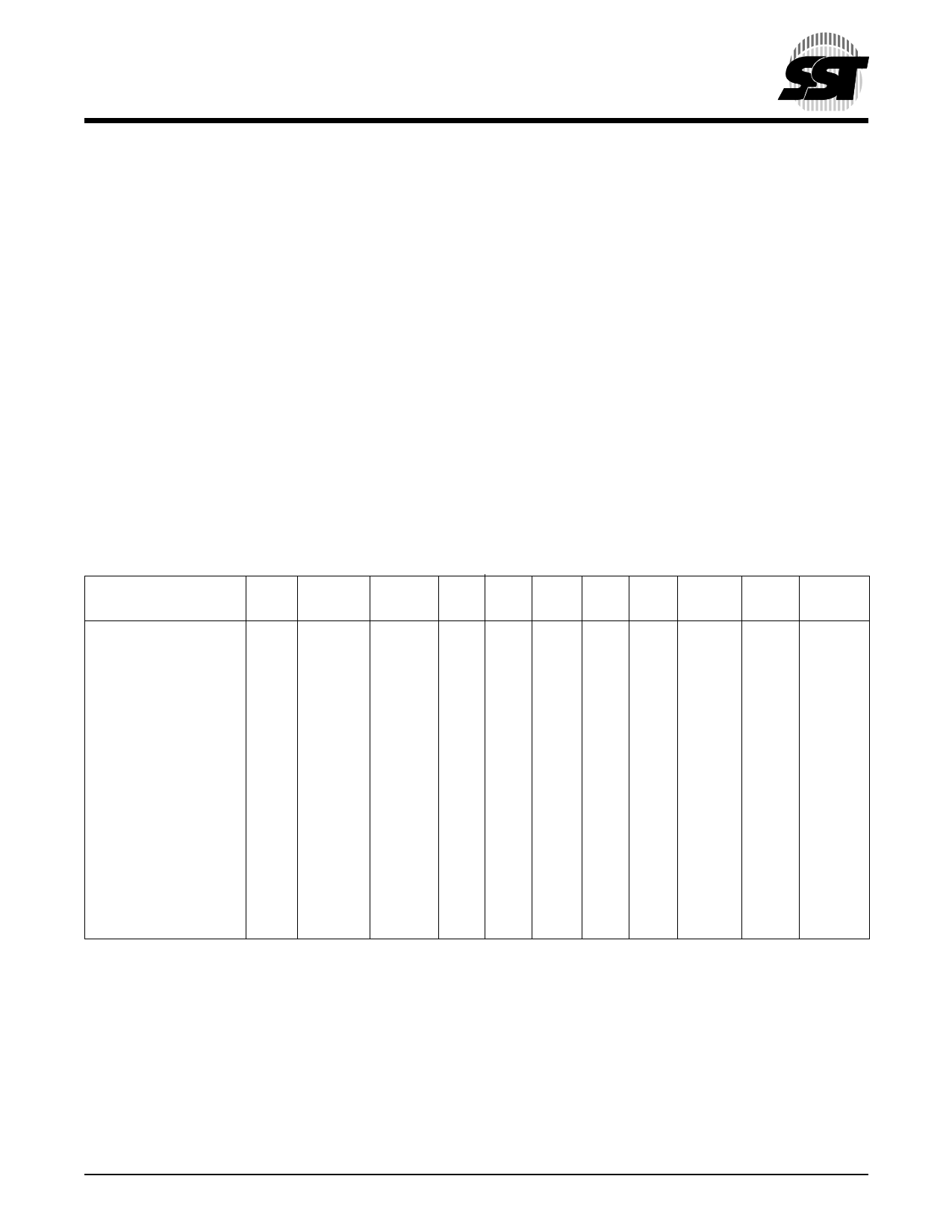

TABLE 4: EXTERNAL HOST MODE COMMANDS

7

Operation

RST PSEN# PROG# EA# P3[7] P3[6] P2[7] P2[6] P0[7:0] P1[7:0] P3[5:4]

/ALE

P2[5:0]

8

READ-ID

H

L

H

HL L

L

L

DO

AL

AH

CHIP-ERASE

BLOCK-ERASE

H

L

H

L

ß

HL L

LH

X

ß

HHH

LH

X

X

X

X A[15:12]

9

SECTOR-ERASE

H

L

ß

HH L

HH

X

AL

AH

BYTE-PROGRAM

H

L

ß

HHH HL

DI

AL

AH

10

BURST-PROGRAM H

L

ß

HLH HL

DI

AL

AH

BYTE-VERIFY

(Read)

PROG-SB1

PROG-SB2

PROG-SB3

PROG-RB0

PROG-RB1

H

L

H

HHH

LL

DO

AL

AH

11

H

L

ß

HHH HH

X

X

X

H

L

ß

HL L

HH

X

X

X

12

H

L

ß

HLH

LH

X

X

X

H

L

ß

HH L

LL

X

X

X

13

H

L

ß

HH L

LH

X

X

X

Note: Symbol ß signifies a negative pulse and the command is asserted during the low state of PROG#/ALE input. All other

combinations of the above input pins are invalid and may result in unexpected behaviors.

Note: L = Logic low level; H = Logic high level; X = Don‘t care; AL = Address low order byte; AH = Address high order byte;

DI = Data Input; DO = Data Output; A[15:12] = 0xxxb for Block 0 and A[15:12} = “Fh” for Block 1.

344 PGM T4.4

14

15

16

© 2000 Silicon Storage Technology, Inc.

19

344-2 8/00