VP551E View Datasheet(PDF) - Mitel Networks

Part Name

Description

View to exact match

VP551E Datasheet PDF : 16 Pages

| |||

VP531E/VP551E

SLAVE2

HCNT7-0

GPSCTL

FSC4SEL

GENDITH

GENLKEN

NOLOCK

PALIDEN

TSURST

CHRMCLIP

TRSEL

H &V Slave position register

Adjusts for delay at which pixel data

occurs relative to HS

GPS Control

When high, REFSQ = 4xFSC and GPP

bit D6 is forced to become an input for a

SCSYNC signal (high = reset), which

provides a synchronous phase reset for

FSC divider. Low = normal operation with

REFSQ = 1xFSC. (default).

1 = Gen lock dither added.

High = enable Genlock to REFSQ signal

input.

Low = internal subcarrier generation

(default).

Genlock status bit (read only)

Low = Genlocked.

High = cannot lock to REFSQ. This bit is

cleared by reading and set again if lock

cannot be attained.

High = enable external PAL ID phase

control and GPP bit D7 is forced to

become an input for PAL ID switch signal,

(GPP bit D7 - Low = +135°,

High = -135°).

Low = normal operation, internal PAL ID

phase switch is used (default).

High = chip soft reset. Registers are NOT

reset to default values.

Low = normal operation (default).

High = enable clipping of chroma data

when luma goes below black level and is

clipped.

Low = no chroma clipping (default).

High = master mode, GPP bits D0 - 4 are

forced to become a video timing port with

VS, HS and FIELD outputs.

Low = slave mode, timing from REC656.

I2C BUS CONTROL INTERFACE

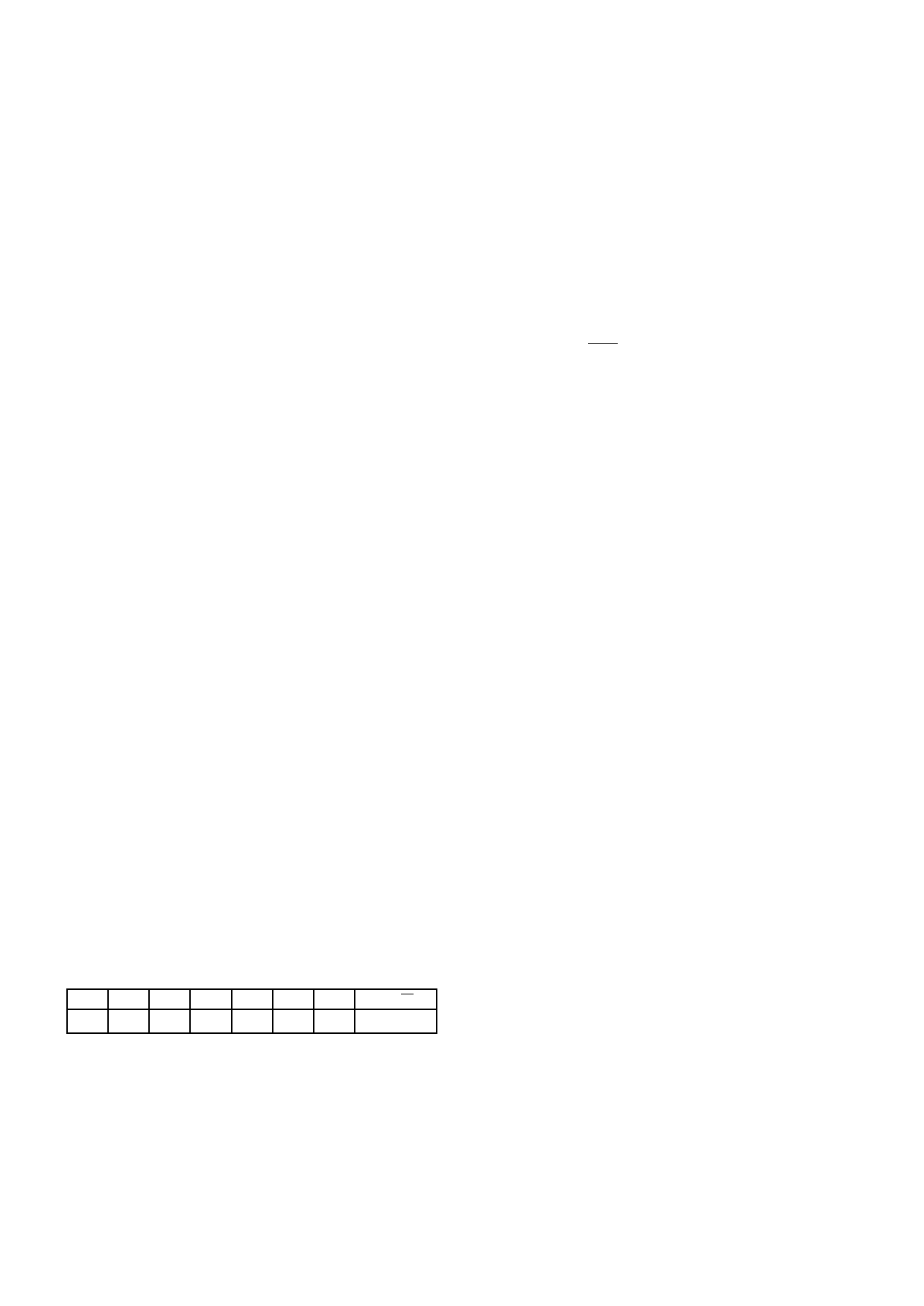

I2C bus address

A6 A5 A4 A3 A2 A1 A0

0 0 0 1 1 SA2 SA1

R/ W

X

The serial microprocessor interface is via the bi-

directional port consisting of a data (SDA) and a clock (SCL)

line. It is compatible to the Philips I2C bus standard (Jan. 1992

publication number 9398 393 40011). The interface is a slave

transmitter - receiver with a sub-address capability. All

communication is controlled by the microprocessor. The SCL

line is input only. The most significant bit (MSB) is sent first.

Data must be stable during SCL high periods.

8

A bus free state is indicated by both SDA and SCL lines

being high. START of transmission is indicated by SDA being

pulled low while SCL is high. The end of transmission, referred

to as a STOP, is indicated by SDA going from low to high while

SCL is high. The STOP state can be omitted if a repeated

START is sent after the acknowledge bit. The reading device

acknowledges each byte by pulling the SDA line low on the

ninth clock pulse, after which the SDA line is released to allow

the transmitting device access to the bus.

The device address can be partially programmed by the

setting of the pins SA1 and SA2. This allows the device to

respond to one of four addresses, providing for system

flexibility. The I2C bus address is seven bits long with the last

bit indicating read / write for subsequent bytes.

The first data byte sent after the device address, is the sub-

address - BAR (base address register). The next byte will be

written to the register addressed by BAR and subsequent

bytes to the succeeding registers. The BAR maintains its data

after a STOP signal.

NTSC/PAL Video Standards

Both NTSC (4-field, 525 lines) and PAL (8-field, 625 lines)

video standards are supported by the VP531/VP551. All

raster synchronisation, colour sub-carrier and burst

characteristics are adapted to the standard selected. The

VP531/VP551 generates outputs which follow the

requirements of SMPTE 170M and CCIR 624 for PAL signals.

The device supports the following:

NTSC,

PAL B, D, G, H, I, N (Argentina).

TRS - Slave mode

The VP531 has an internal timing generator which

produces video timing signals appropriate to the mode of

operation. In the default (power up) slave mode, all timing

signals are derived from the input clock, PXCK, which must be

derived from a crystal controlled oscillator. Input pixel data is

latched on the rising edge of the PXCK clock.

The video timing generator produces the internal blanking

and burst gate pulses, together with the composite sync

output signal, using timing data (TRS codes) from the

Ancillary data stream in the REC656 input signal, (when

TRSEL (bit 0 of GPSCTL register) is set low).

Slave H & V mode

H & V slave mode is enabled by setting the SL_H&V bit in

the GCR register. In this mode the position of the video syncs

is derived from the HS and VS inputs. These GPP pins are

automatically configured as inputs when SL_H&V is set to '1'.

This mode requires 262/263 line syncs in NTSC mode (not

262.5/262.5) and 312/313 syncs in PAL. The VSYNC and

negative edges HSYNC need to be aligned. When

programming the SLH&V bit needs setting first and then the

TRSEL bit in reg FF, otherwise there will be a clash of outputs.

The VSYNC is input to pin 3 and the HSYNC to pin 4 both at

5V TTL levels.

HCNT

To ensure that the incoming data is sampled correctly a 10

bit binary number (HCNT) has to be programmed into the

SLAVE1 and 2 registers. This will allow the device's internal

horizontal counter to align with the video data, each bit