CY7C4221V-25JC View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

View to exact match

CY7C4221V-25JC Datasheet PDF : 16 Pages

| |||

CY7C4421V/4201V/4211V/4221V

PRELIMINARY

CY7C4231V/4241V/4251V

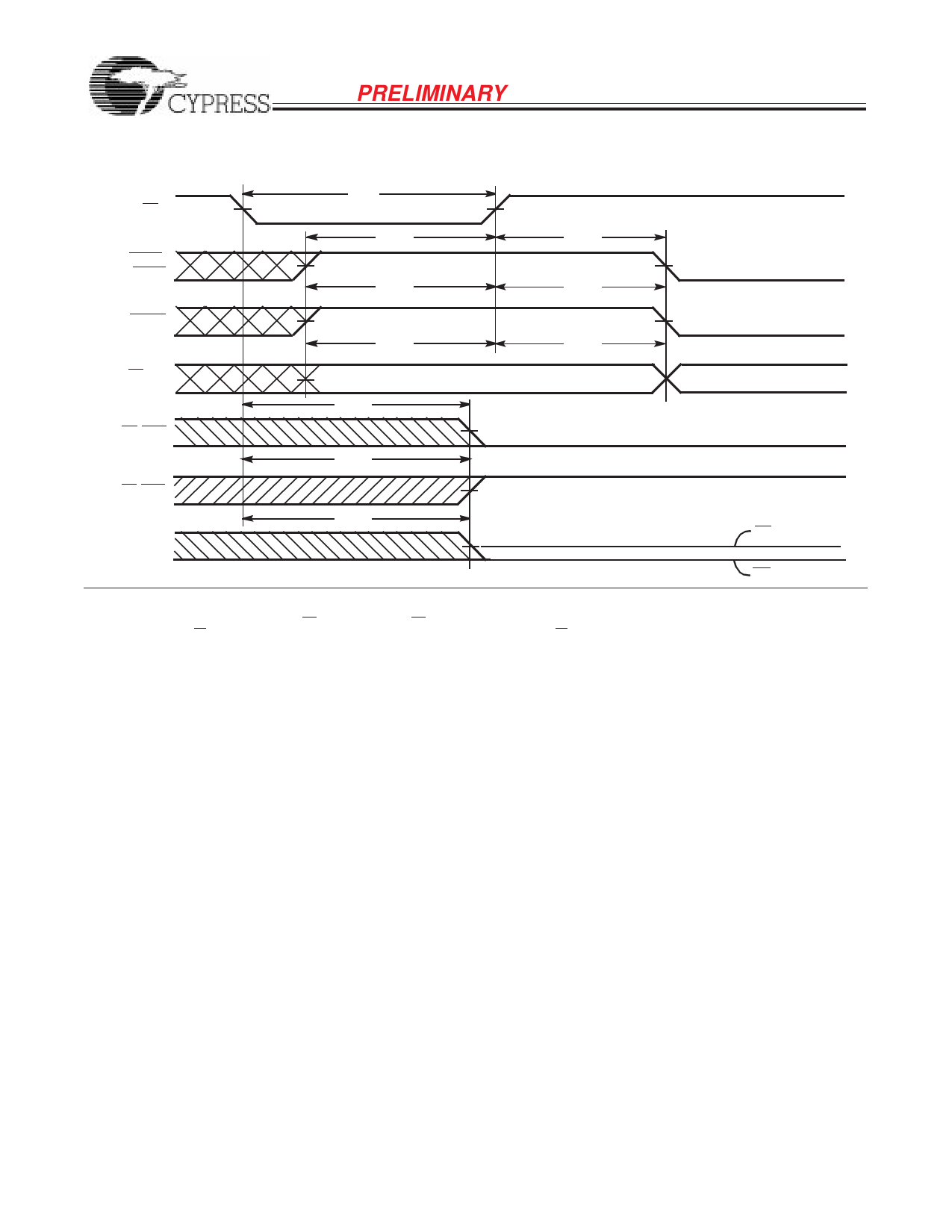

Switching Waveforms (continued)

Reset Timing[11]

tRS

RS

REN1,

REN2

tRSS

tRSS

tRSR

tRSR

WEN1

WEN2/LD [13]

tRSS

tRSR

EF,PAE

tRSF

tRSF

FF,PAF,

Q0 − Q8

tRSF

OE=1 [12]

OE=0

42X1V–8

Notes:

11. The clocks (RCLK, WCLK) can be free-running during reset.

12. After reset, the outputs will be LOW if OE = 0 and three-state if OE=1.

13. Holding WEN2/LD HIGH during reset will make the pin act as a second enable pin. Holding WEN2/LD LOW during reset will make the pin act as a load enable for the

programmable flag offset registers.

6