NT35510 View Datasheet(PDF) - Novatek Microelectronics

Part Name

Description

View to exact match

NT35510 Datasheet PDF : 211 Pages

| |||

PRELIMINARY

NT35510

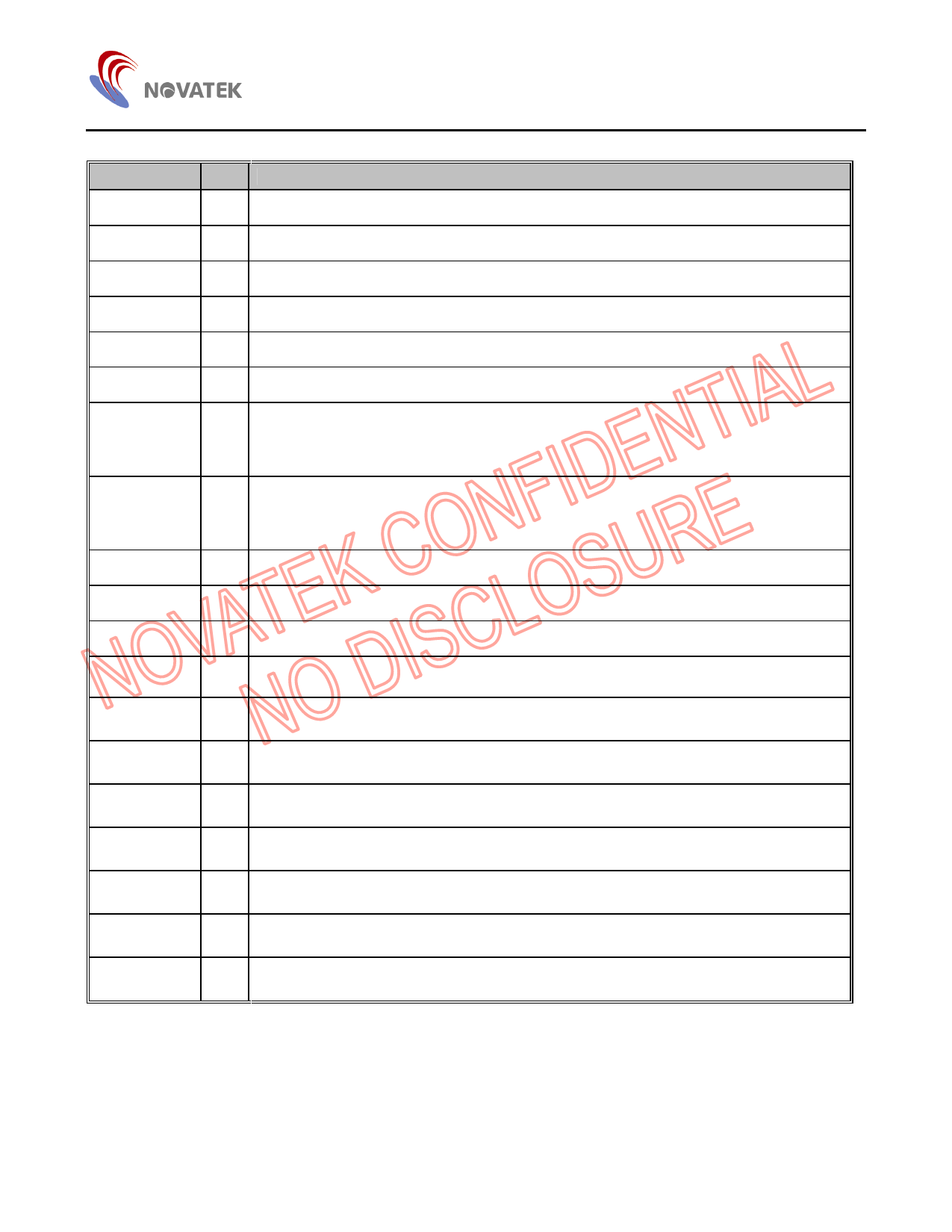

4.8 DC/DC Converter Pins

Symbol

AVDD

AVEE

VCL

VGH

VGLX

VGL

C11P, C11N

C12P, C12N

C13P, C13N

C14P, C14N

C21P, C21N

C22P, C22N

C23P, C23N

C24P, C24N

C31P, C31N

C32P, C32N

C41P, C41N

C51P, C51N

VRGH

I/O

Description

O

Output voltage from step-up circuit 1, generated from VDDB.

Connect a capacitor for stabilization.

O

Output voltage from step-up circuit 2, generated from VDDB.

Connect a capacitor for stabilization.

O

Output voltage from step-up circuit 3, generated from VDDB.

Connect a capacitor for stabilization.

O

Output voltage from step-up circuit 4.

Connect a capacitor for stabilization.

O

Output voltage from step-up circuit 5.

Connect a capacitor for stabilization.

I

Substrate voltage for driver IC.

Please connect VGL to VGLX.

O

Capacitor connection pins for the step-up circuit which generate AVDD.

Connect capacitor as requirement. When not in used, please open these pins.

O

Capacitor connection pins for the step-up circuit which generate AVEE.

Connect capacitor as requirement. When not in used, please open these pins.

O

Capacitor connection pins for the step-up circuit which generate VCL.

Connect capacitor as requirement.

O

Capacitor connection pins for the step-up circuit which generate VGH.

Connect capacitor as requirement.

O

Capacitor connection pins for the step-up circuit which generate VGLX.

Connect capacitor as requirement.

O

Output voltage generated from AVDD.

Connect a capacitor for stabilization. When not in use, please open this pin.

VGL_REG

O

Output voltage generated from VGLX. LDO output used for panel voltage.

Connect a capacitor for stabilization. When not in use, please open this pin.

EXTP

O

PFM1 control output for DC/DC converter to generate AVDD.

Connect to gate of external NMOS device. When not in use, please open this pin.

EXTN

O

PFM2 control output for DC/DC converter to generate AVEE.

Connect to gate of external PMOS device. When not in use, please open this pin.

CSP

I

Current sensing input for PFM1 DC/DC converter (generate AVDD).

When not in use, please connect to VSSB.

CSN

I

Current sensing input for PFM2 DC/DC converter (generate AVEE).

When not in use, please connect to VSSB.

VREF_PWR

O

Regulator output for power voltage.

Connect a capacitor for stabilization.

VREFCP

O

Reference voltage for internal voltage generating circuit.

Connect capacitor for stabilization.

11/8/2010

19

Version 0.00

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability,

fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such

information.