SP8400 View Datasheet(PDF) - Zarlink Semiconductor Inc

Part Name

Description

View to exact match

SP8400 Datasheet PDF : 5 Pages

| |||

SP8400

Very Low Phase Noise Synthesiser Divider

The SP8400 is a very low phase noise programmable

divider which is based on a divide by 8/9 dual modulus

prescaler and a 12 stage control counter. This gives a

minimum division ratio of 56 (64 for fractional - N synthesis

applications), and a maximum division ratio of 4103. Special

circuit techniques have been used to reduce the phase noise

considerably below that produced by standard dividers.The

data inputs are CMOS or TTL compatible.

The SP8400 is packaged in a 28 pin plastic SO package.

FEATURES

I Very low Phase Noise (Typically -156dBc/Hz at 1kHz

offset)

I Supply Voltage 5V

ABSOLUTE MAXIMUM RATINGS

Supply Voltage

Output Current

Storage Temperature Range

Maximum Clock Input Voltage

6.5V

20mA

-55°C to +125°C

2.5V p-p

Ordering Information

September 2005

SP8400/KG/MPES 28 Pin SOIC Tubes

SP8400/KG/MPFP 28 Pin SOIC* Tubes

*Pb Free Matte Tin

M2

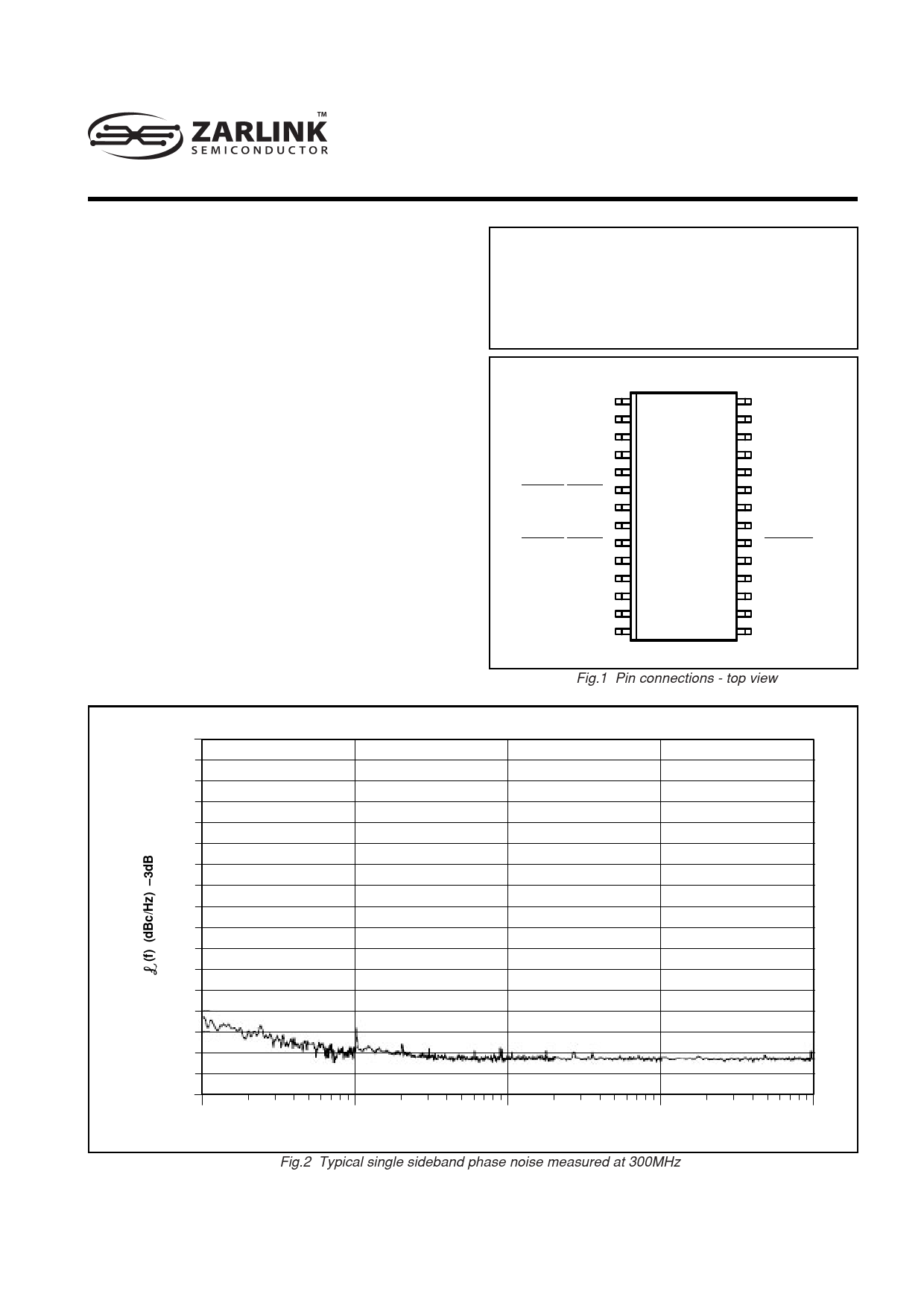

1

M1

2

M0

3

VCC +5V

4

GND

5

CLOCK INPUT

6

CLOCK INPUT

7

CLOCK INPUT

8

CLOCK INPUT

9

GND

10

VCC +5V

11

VCC +5V

12

GND

13

A0

14

28

M3

27

M4

26

M5

25

M6

24

M7

23

M8

22

N/C

21

OUTPUT

20

OUTPUT

19

N/C

18

VCC +5V

17

N/C

16

A2

15

A1

MP28

Fig.1 Pin connections - top view

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

–140

–150

–160

–170

10

100

1k

10k

Frequency (Hz)

Fig.2 Typical single sideband phase noise measured at 300MHz

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 1997-2005, Zarlink Semiconductor Inc. All Rights Reserved.

100k