ADUC812(1999) View Datasheet(PDF) - Analog Devices

Part Name

Description

View to exact match

ADUC812 Datasheet PDF : 31 Pages

| |||

ADuC812

ADuC812 ARCHITECTURE, MAIN FEATURES

The ADuC812 is a highly integrated high accuracy 12-bit data

acquisition system. At its core, the ADuC812 incorporates a high

performance 8-bit (8051-Compatible) MCU with on-chip repro-

grammable nonvolatile Flash/EE program memory controlling a

multichannel (8-input channels), 12-bit ADC.

The chip incorporates all secondary functions to fully support the

programmable data acquisition core. These secondary functions

include User Flash/EE Data Memory, Watchdog Timer (WDT),

Power Supply Monitor (PSM) and various industry-standard

parallel and serial interfaces.

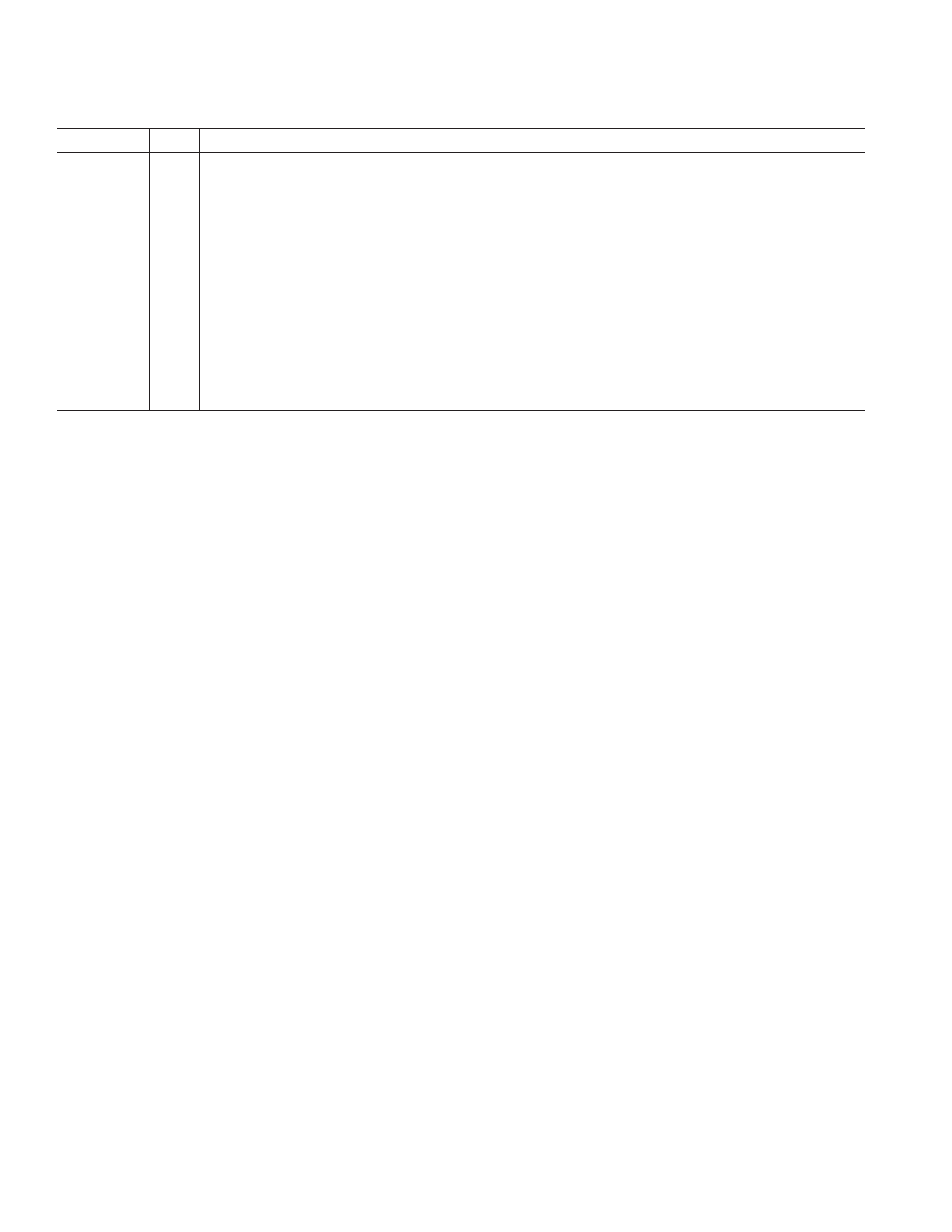

ADuC812 MEMORY ORGANIZATION

As with all 8051-compatible devices, the ADuC812 has separate

address spaces for Program and Data memory as shown in Fig-

ure 1. Also as shown in Figure 1, an additional 640 Bytes of

Flash/EE Data Memory are available to the user. The Flash/EE

Data Memory area is accessed indirectly via a group of control

registers mapped in the Special Function Register (SFR) area.

PROGRAM MEMORY SPACE

READ ONLY

FFFFFFH

EXTERNAL

PROGRAM

MEMORY

SPACE

The lower 128 bytes of internal data memory are mapped as

shown in Figure 2. The lowest 32 bytes are grouped into four

banks of eight registers addressed as R0 through R7. The next

16 bytes (128 bits) above the register banks form a block of bit

addressable memory space at bit addresses 00H through 7FH.

The SFR space is mapped in the upper 128 bytes of internal

data memory space. The SFR area is accessed by direct address-

ing only and provides an interface between the CPU and all on-

chip peripherals. A block diagram showing the programming

model of the ADuC812 via the SFR area is shown in Figure 3.

7FH

30H

BANKS

SELECTED

VIA

BITS IN PSW

20H

11

18H

10

10H

01

08H

00

00H

2FH

BIT-ADDRESSABLE SPACE

(BIT ADDRESSES 0–7FH)

1FH

17H

4 BANKS OF 8 REGISTERS

0FH

R0–R7

07H

RESET VALUE OF

STACK POINTER

2000H

Figure 2. Lower 128 Bytes of Internal RAM

EA = 1

INTERNAL

8K BYTE

FLASH/EE

PROGRAM

MEMORY

1FFFH

0000H

EA = 0

EXTERNAL

PROGRAM

MEMORY

SPACE

DATA MEMORY SPACE

READ/WRITE

9FH

(PAGE 159)

640 BYTES

FLASH/EE DATA

MEMORY

ACCESSED

INDIRECTLY

VIA SFR

CONTROL REGISTERS

00H

(PAGE 0)

FFFFFFH

INTERNAL

DATA MEMORY

SPACE

FFH

UPPER

128

80H

7FH

LOWER

128

00H

ACCESSIBLE

BY

INDIRECT

ADDRESSING

ONLY

ACCESSIBLE

BY

DIRECT

AND

INDIRECT

ADDRESSING

SPECIAL FFH

FUNCTION

REGISTERS

ACCESSIBLE

BY DIRECT

ADDRESSING

ONLY

80H

000000H

EXTERNAL

DATA

MEMORY

SPACE

(24-BIT

ADDRESS

SPACE)

Figure 1. ADuC812 Program and Data Memory Maps

8K BYTE

ELECTRICALLY

REPROGRAMMABLE

NONVOLATILE

FLASH/EE PROGRAM

MEMORY

8051-

COMPATIBLE

CORE

128-BYTE

SPECIAL

FUNCTION

REGISTER

AREA

640-BYTE

ELECTRICALLY

REPROGRAMMABLE

NONVOLATILE

FLASH/EE DATA

MEMORY

SELF-CALIBRATING

8-CHANNEL

HIGH SPEED

12-BIT ADC

OTHER ON-CHIP

PERIPHERALS

TEMPERATURE

SENSOR

2 ؋ 12-BIT DACs

SERIAL I/O

PARALLEL I/O

WDT

PSM

Figure 3. ADuC812 Programming Model

ADC CIRCUIT INFORMATION

General Overview

The ADC conversion block incorporates a 5 µs, 8-channel,

12-bit, single supply A/D converter. This block provides the

user with multichannel mux, track/hold, on-chip reference,

calibration features and A/D converter. All components in this

block are easily configured via a 3-register SFR interface.

The A/D converter consists of a conventional successive-

approximation converter based around a capacitor DAC. The

converter accepts an analog input range of 0 to +VREF. A high

precision, low drift and factory calibrated 2.5 V reference is

–8–

REV. 0