SST89E52RD-33-C-NI View Datasheet(PDF) - Silicon Storage Technology

Part Name

Description

View to exact match

SST89E52RD-33-C-NI Datasheet PDF : 81 Pages

| |||

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

Data Sheet

3.2 Program Memory Block Switching

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be

used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

TABLE 3-1: SFCF Values for Program Memory Block Switching

SFCF[1:0]

10, 11

01

00

Program Memory Block Switching

Block 1 is not visible to the PC;

Block 1 is reachable only via in-application programming from E000H - FFFFH.

Both Block 0 and Block 1 are visible to the PC.

Block 0 is occupied from 0000H - 7FFFH. Block 1 is occupied from E000H - FFFFH.

Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.

When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.

Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through

in-application programming.

T3-1.0 1255

3.2.1 Reset Configuration of Program Memory

Block Switching

Program memory block switching is initialized after reset

according to the state of the Start-up Configuration bit SC0

and/or SC1. The SC0 and SC1 bits are programmed via

an external host mode command or an IAP Mode com-

mand. See Table 4-2.

Once out of reset, the SFCF[0] bit can be changed dynam-

ically by the program for desired effects. Changing SFCF[0]

will not change the SC0 bit.

Caution must be taken when dynamically changing the

SFCF[0] bit. Since this will cause different physical memory

to be mapped to the logical program address space. The

user must avoid executing block switching instructions

within the address range 0000H to 1FFFH.

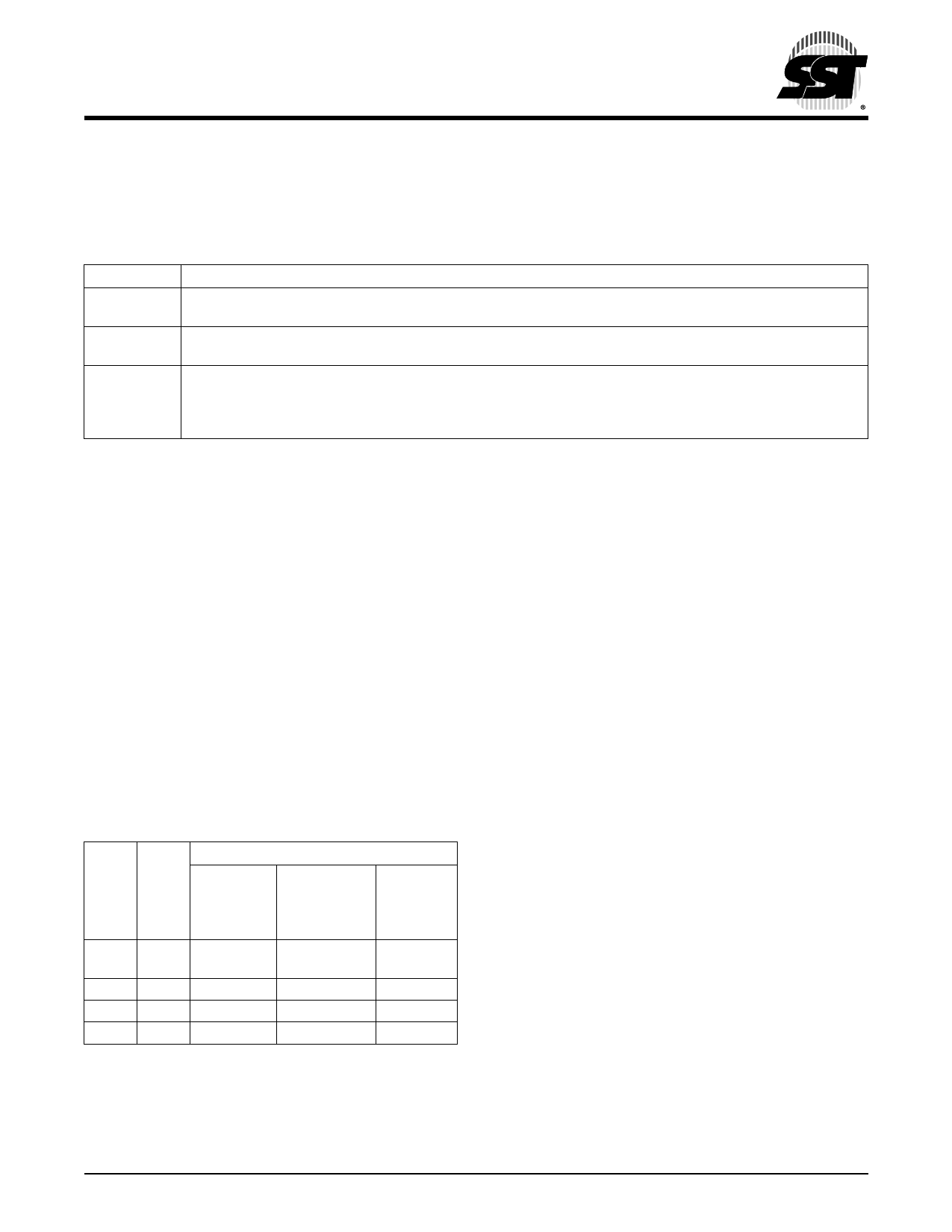

TABLE 3-2: SFCF Values Under Different Reset

Conditions

State of SFCF[1:0] after:

SC11 SC01

U (1) U (1)

U (1)

P (0)

P (0)

P (0)

U (1)

P (0)

Power-on

or

External

Reset

00

(default)

01

10

11

WDT Reset

or

Brown-out

Reset

x0

x1

10

11

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

Software

Reset

10

11

10

11

T3-2.0 1255

3.3 Data RAM Memory

The data RAM has 1024 bytes of internal memory. The

RAM can be addressed up to 64KB for external data

memory.

3.4 Expanded Data RAM Addressing

The SST89E/V5xRDx both have the capability of 1K of

RAM. See Figure 3-4.

The device has four sections of internal data memory:

1. The lower 128 Bytes of RAM (00H to 7FH) are

directly and indirectly addressable.

2. The higher 128 Bytes of RAM (80H to FFH) are

indirectly addressable.

3. The special function registers (80H to FFH) are

directly addressable only.

4. The expanded RAM of 768 Bytes (00H to 2FFH) is

indirectly addressable by the move external

instruction (MOVX) and clearing the EXTRAM bit.

(See “Auxiliary Register (AUXR)” in Section 3.6,

“Special Function Registers”)

Since the upper 128 bytes occupy the same addresses as

the SFRs, the RAM must be accessed indirectly. The RAM

and SFRs space are physically separate even though they

have the same addresses.

When instructions access addresses in the upper 128

bytes (above 7FH), the MCU determines whether to

access the SFRs or RAM by the type of instruction given. If

it is indirect, then RAM is accessed. If it is direct, then an

SFR is accessed. See the examples below.

©2006 Silicon Storage Technology, Inc.

13

S71255-05-000

5/06