UPD45128163-I-E View Datasheet(PDF) - Elpida Memory, Inc

Part Name

Description

View to exact match

UPD45128163-I-E

UPD45128163-I-E Datasheet PDF : 86 Pages

| |||

µPD45128163-I-E

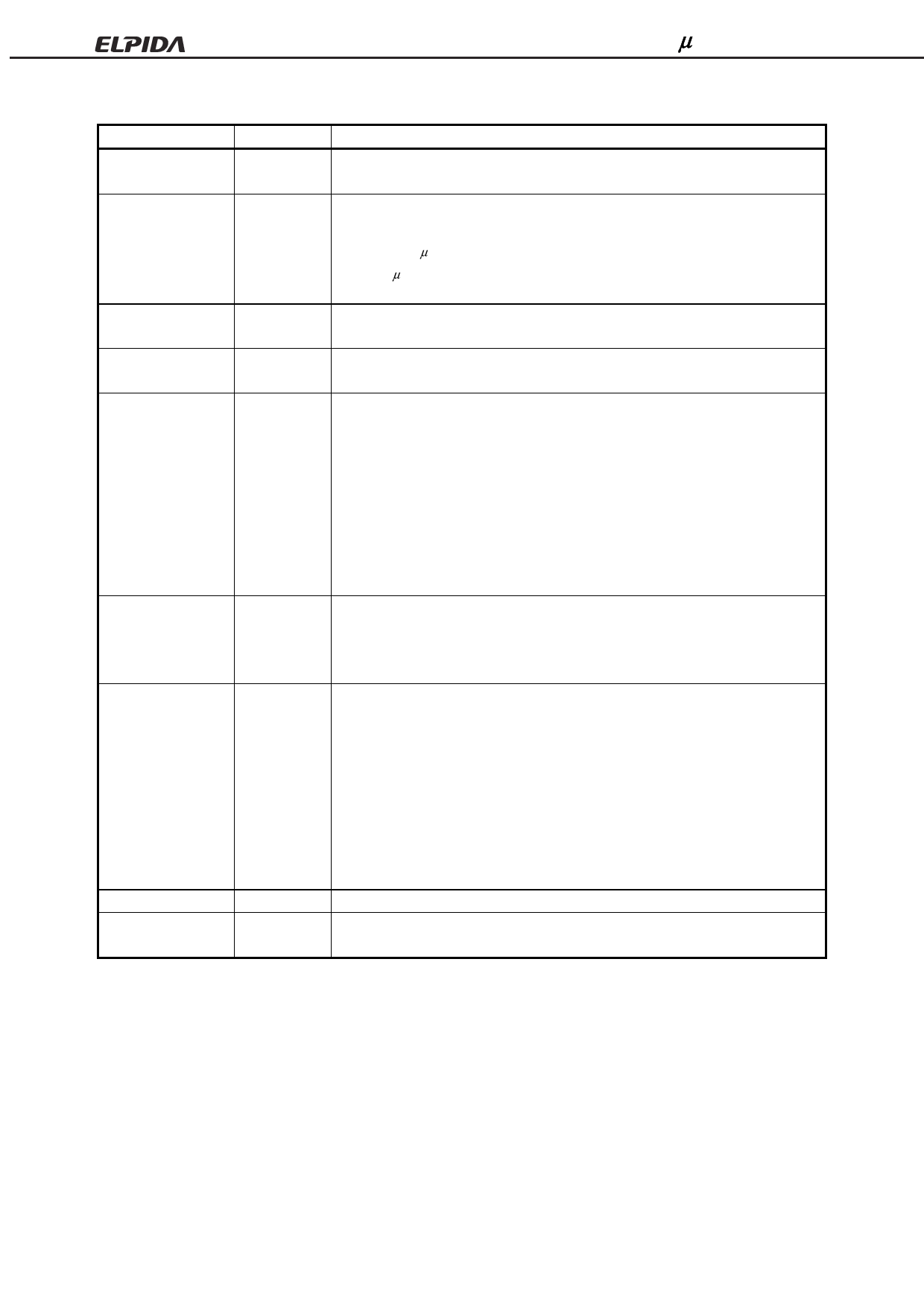

1. Input / Output Pin Function

Pin name

CLK

CKE

/CS

/RAS, /CAS, /WE

A0 - A11

BA0, BA1

UDQM, LDQM

DQ0 - DQ15

VCC, VSS, VCCQ, VSSQ

Input / Output

Function

Input

Input

Input

Input

Input

CLK is the master clock input. Other inputs signals are referenced to the CLK rising

edge.

CKE determine validity of the next CLK (clock). If CKE is high, the next CLK rising edge

is valid; otherwise it is invalid. If the CLK rising edge is invalid, the internal clock is not

issued and the µPD45128xxx suspends operation.

When the µPD45128xxx is not in burst mode and CKE is negated, the device enters

power down mode. During power down mode, CKE must remain low.

/CS low starts the command input cycle. When /CS is high, commands are ignored but

operations continue.

/RAS, /CAS and /WE have the same symbols on conventional DRAM but different

functions. For details, refer to the command table.

Row Address is determined by A0 - A11 at the CLK (clock) rising edge in the active

command cycle. It does not depend on the bit organization.

Column Address is determined by A0 - A9, A11 at the CLK rising edge in the read or

write command cycle. It depends on the bit organization: A0 - A8 for ×16 device.

A10 defines the precharge mode. When A10 is high in the precharge command cycle,

all banks are precharged; when A10 is low, only the bank selected by BA0(A13) and

BA1(A12) is precharged.

When A10 is high in read or write command cycle, the precharge starts automatically

after the burst access.

Input

Input

BA0(A13) and BA1(A12) are the bank select signal. In command cycle, BA0(A13) and

BA1(A12) low select bank A, BA0(A13) high and BA1(A12) low select bank B, BA0(A13)

low and BA1(A12) high select bank C and then BA0(A13) and BA1(A12) high select bank

D.

DQM controls I/O buffers. In ×16 products, UDQM and LDQM control upper byte and

lower byte I/O buffers, respectively.

In read mode, UDQM and LDQM controls the output buffers like a conventional /OE pin.

UDQM and LDQM high and UDQM and LDQM low turn the output buffers off and on,

respectively.

The UDQM and LDQM latency for the read is two clocks.

In write mode, UDQM and LDQM controls the word mask. Input data is written to the

memory cell if UDQM and LDQM is low but not if UDQM and LDQM is high.

The UDQM and LDQM latency for the write is zero.

Input / Output DQ pins have the same function as I/O pins on a conventional DRAM.

(Power supply) VCC and VSS are power supply pins for internal circuits. VCCQ and VSSQ are power supply

pins for the output buffers.

8

Data Sheet E0729N10 (Ver. 1.0)