M27W401-100B6TR View Datasheet(PDF) - STMicroelectronics

Part Name

Description

View to exact match

M27W401-100B6TR Datasheet PDF : 15 Pages

| |||

M27W401

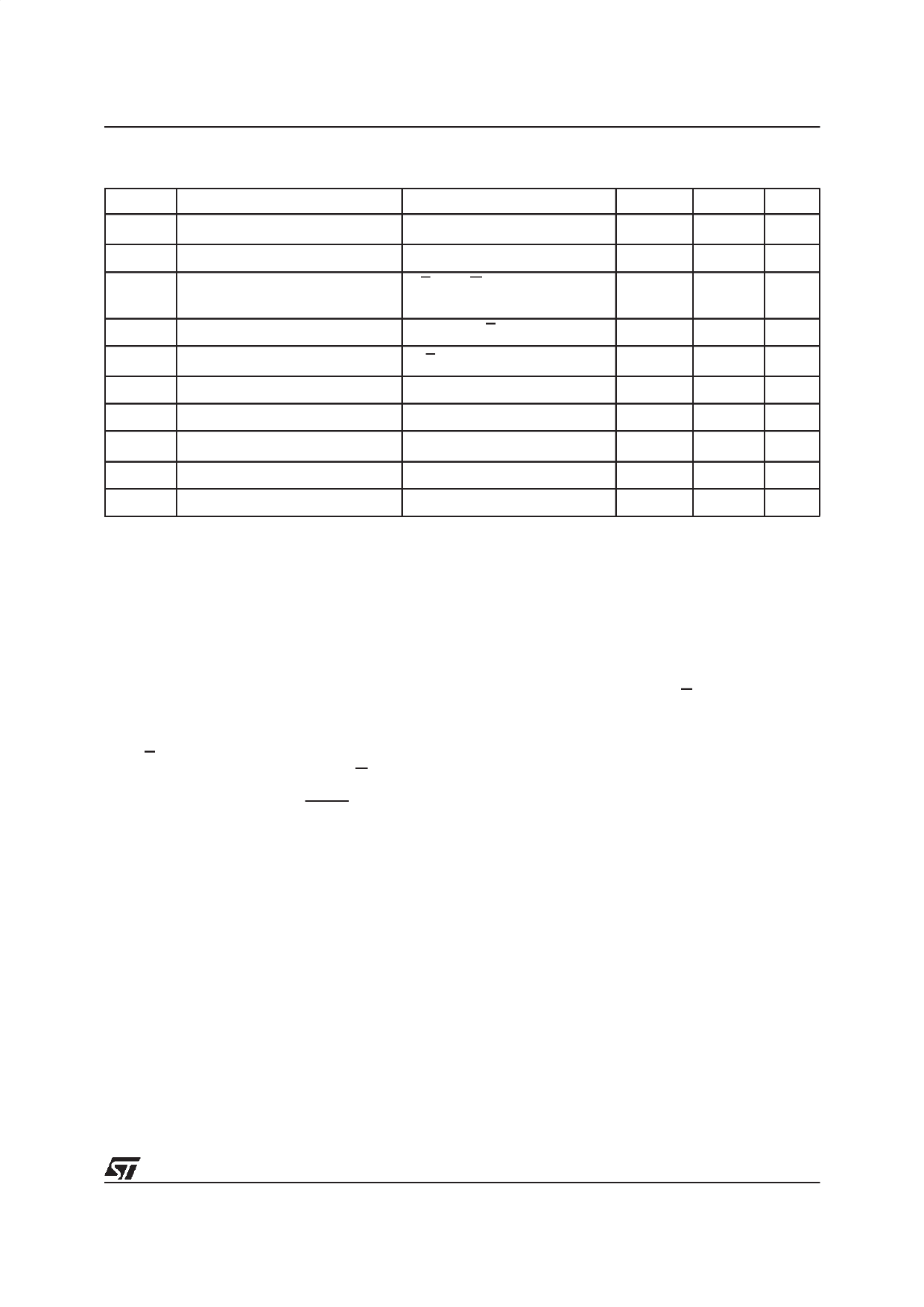

Table 7. Read Mode DC Characteristics (1)

(TA = –40 to 85°C; VCC = 2.7V to 3.6V; VPP = VCC)

Symbol

Parameter

Test Condition

Min

ILI

Input Leakage Current

ILO Output Leakage Current

ICC Supply Current

ICC1 Supply Current (Standby) TTL

0V ≤ VIN ≤ VCC

0V ≤ VOUT ≤ VCC

E = VIL, G = VIL, IOUT = 0mA,

f = 5MHz, VCC ≤ 3.6V

E = VIH

ICC2 Supply Current (Standby) CMOS

IPP Program Current

VIL

Input Low Voltage

E > VCC – 0.2V, VCC ≤ 3.6V

VPP = VCC

–0.6

VIH (2) Input High Voltage

0.7 VCC

VOL Output Low Voltage

IOL = 2.1mA

VOH Output High Voltage TTL

IOH = –400µA

2.4

Note: 1. VCC must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

2. Maximum DC voltage on Output is VCC +0.5V.

Max

±10

±10

15

1

15

10

0.2 VCC

VCC + 0.5

0.4

Unit

µA

µA

mA

mA

µA

µA

V

V

V

V

Two Line Output Control

Because EPROMs are usually used in larger

memory arrays, this product features a 2 line con-

trol function which accommodates the use of mul-

tiple memory connection. The two line control

function allows:

a. the lowest possible memory power dissipation,

b. complete assurance that output bus contention

will not occur.

For the most efficient use of these two control

lines, E should be decoded and used as the prima-

ry device selecting function, while G should be

made a common connection to all devices in the

array and connected to the READ line from the

system control bus. This ensures that all deselect-

ed memory devices are in their low power standby

mode and that the output pins are only active

when data is required from a particular memory

device.

System Considerations

The power switching characteristics of Advanced

CMOS EPROMs require careful decoupling of the

devices. The supply current, ICC, has three seg-

ments that are of interest to the system designer:

the standby current level, the active current level,

and transient current peaks that are produced by

the falling and rising edges of E. The magnitude of

the transient current peaks is dependent on the

capacitive and inductive loading of the device at

the output.

The associated transient voltage peaks can be

suppressed by complying with the two line output

control and by properly selected decoupling ca-

pacitors. It is recommended that a 0.1µF ceramic

capacitor be used on every device between VCC

and VSS. This should be a high frequency capaci-

tor of low inherent inductance and should be

placed as close to the device as possible. In addi-

tion, a 4.7µF bulk electrolytic capacitor should be

used between VCC and VSS for every eight devic-

es. The bulk capacitor should be located near the

power supply connection point.The purpose of the

bulk capacitor is to overcome the voltage drop

caused by the inductive effects of PCB traces.

5/15