MC74HC195N View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

View to exact match

MC74HC195N Datasheet PDF : 7 Pages

| |||

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

4-Bit Universal Shift Register

High–Performance Silicon–Gate CMOS

The MC74HC195 is identical in pinout to the LS195. The device inputs are

compatible with standard CMOS outputs, with pull up resistors, they are

compatible with LSTTL outputs.

This static shift register features parallel load, serial load (shift right), hold,

and reset modes of operation. These modes are tabulated in the Function

Table, and further explanation can be found in the Pin Description section.

• Output Drive Capability: 10 LSTTL Loads

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2 to 6 V

• Low Input Current: 1 µA

• High Noise Immunity Characteristic of CMOS Devices

• In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

• Chip Complexity: 150 FETs or 37.5 Equivalent Gates

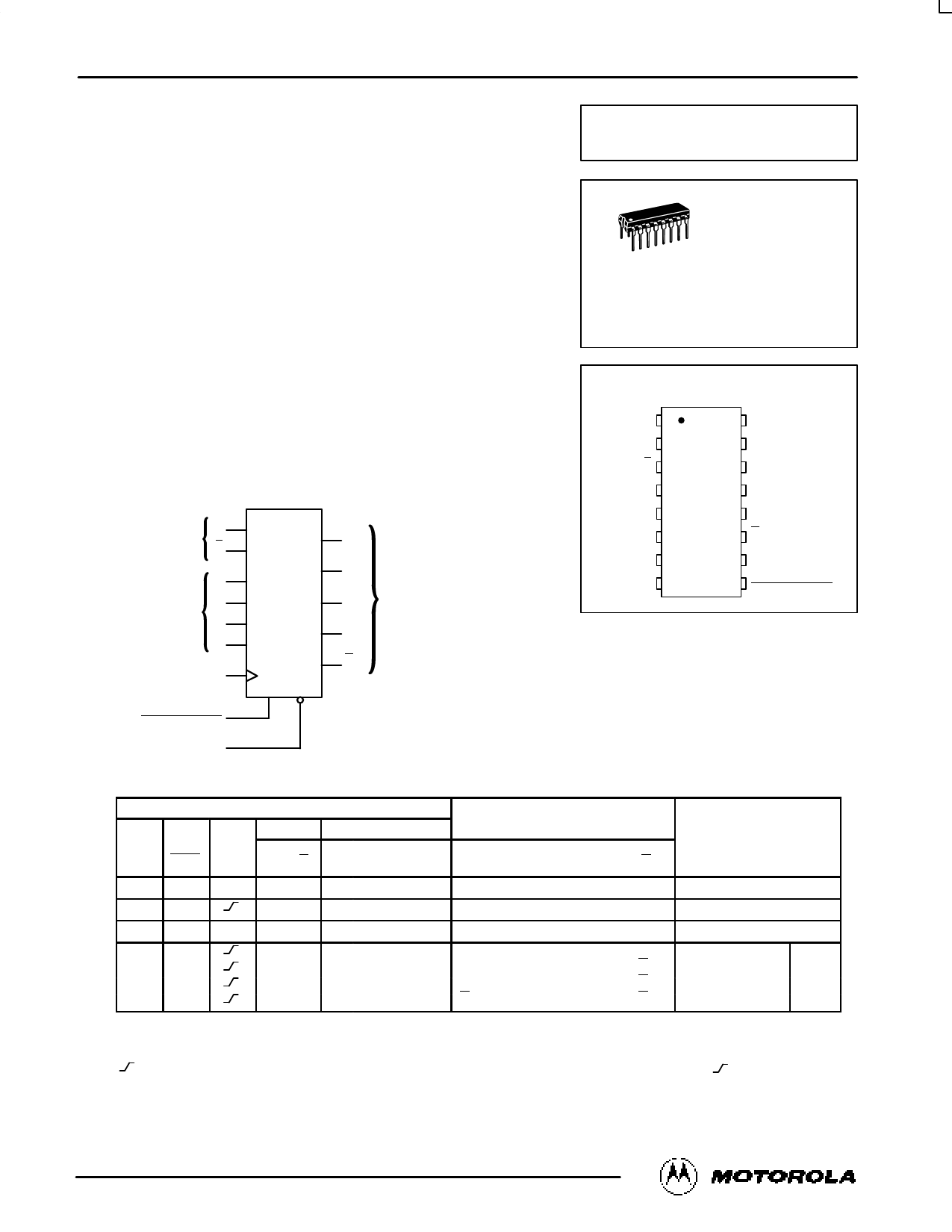

LOGIC DIAGRAM

SERIAL DATA J 2

INPUTS

K3

PARALLEL

DATA

INPUTS

A4

B5

C6

D7

CLOCK 10

15 QA

14 QB

QC

12 QD

11 QD

PARALLEL

DATA

OUTPUTS

MC74HC195

16

1

N SUFFIX

PLASTIC PACKAGE

CASE 648–08

ORDERING INFORMATION

MC74HCXXXN

Plastic

PIN ASSIGNMENT

RESET 1

J2

K3

A4

B5

C6

D7

GND 8

16 VCC

15 QA

14 QB

13 QC

12 QD

11 QD

10 CLOCK

9 SERIAL SHIFT/

PARALLEL LOAD

SERIAL SHIFT/ 9

PARALLEL LOAD

RESET 1

PIN 16 = VCC

PIN 8 = GND

FUNCTION TABLE

Inputs

Serial

Parallel

Outputs

Shift/

Reset Load Clock J K A B C D QA QB QC QD QD

L

X

X XXXXXX L

L

L

L

H

Operating Mode

Reset

H

L

XXa b c d a

b

c

d

d

Parallel Load

H

H

L XXXXXX

No Change

Hold

H

H

H

H

H

H

H

H

L H X X X X QA0 QA0 QBn QCn QCn Retain First Stage Serial

L LXXXX

L QAn QBn QCn QCn Reset First Stage Shift

H H X X X X H QAn QBn QCn QCn Set First Stage

H L X X X X QAn QAn QBn QCn QCn Toggle First Stage

H = high level (steady state)

L = low level (steady state)

X = don’t care

= transition from low to high level.

a, b, c, d = the level of steady–state input at inputs

A, B, C, or D, respectively.

QA0 = the level of QA before the indicated steady–state

input conditions were established.

QAn, QBn, QCn = the level of QA, QB, or QC,

respectively, before the most recent transition

of the clock.

10/95

© Motorola, Inc. 1995

3–1

REV 6