CY7C4425-35AI View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

View to exact match

CY7C4425-35AI Datasheet PDF : 25 Pages

| |||

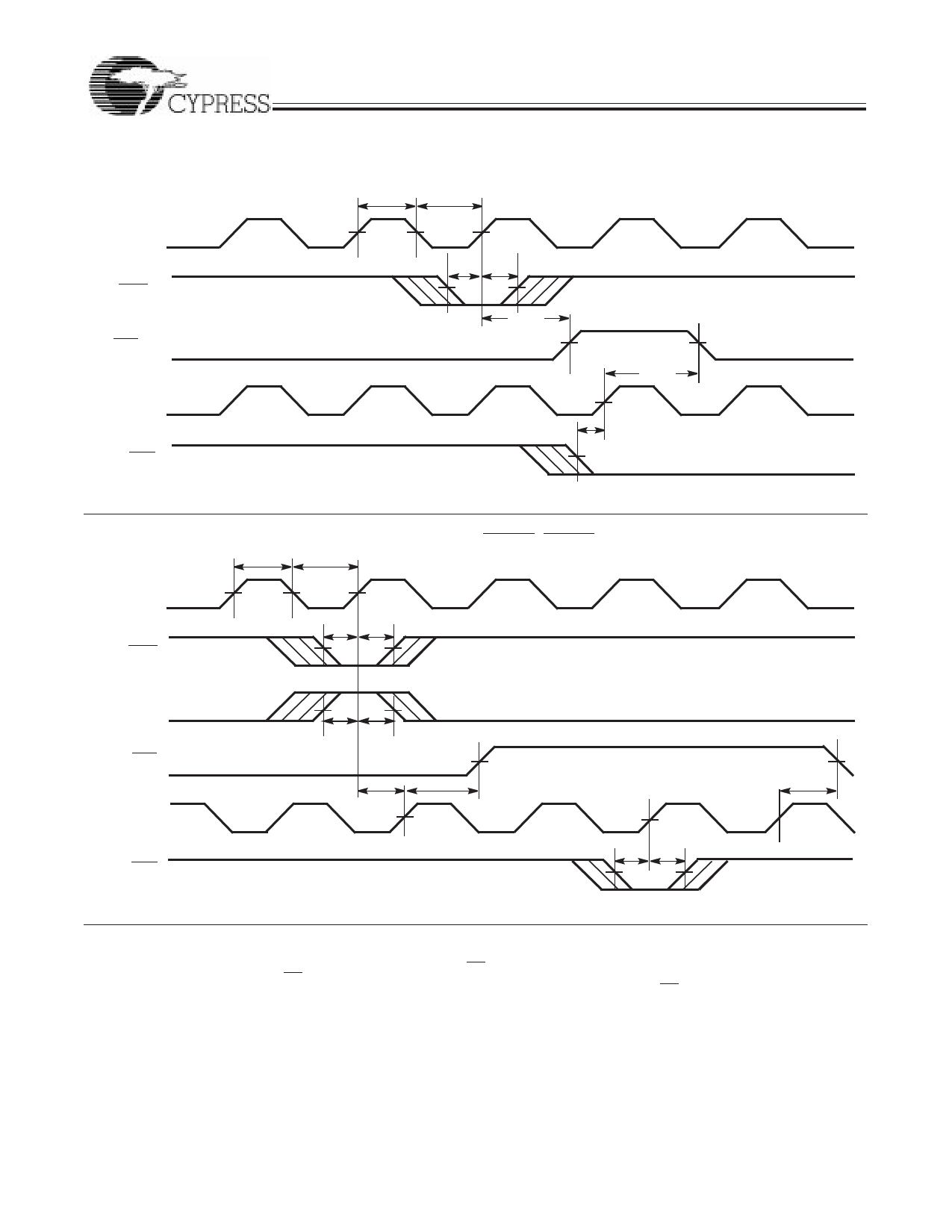

Switching Waveforms (continued)

Programmable Almost Empty Flag Timing

tCLKH

WCLK

WEN

PAE][19]

RCLK

REN

CY7C4425/4205/4215

CY7C4225/4235/4245

tCLKL

tENS tENH

tPAE

n+1 WORDS

IN FIFO

tPAE

tENS

n WORDS IN FIFO

42X5–13

Programmable Almost Empty Flag Timing (applies only in SMODE (SMODE is LOW)

tCLKH

tCLKL

WCLK

WEN

tENS tENH

WEN2

PAE

RCLK

REN

tENS tENH

tSKEW3 [21]

Note

20

tPAEsynch

N + 1 WORDS

INFIFO

tENS

tENS tENH

Note

22

tPAEsynch

42X5–14

Notes:

19. PAE offset – n. Number of data words into FIFO already = n.

20. PAE offset – n.

21. tSKEW3 is the minimum time between a rising WCLK and a rising RCLK edge for PAE to change state during that clock cycle. If the time between the edge of WCLK and the

rising RCLK is less than tSKEW3, then PAE may not change state until the next RCLK.

22. If a read is performed on this rising edge of the read clock, there will be Empty + (n – 1) words in the FIFO when PAE goes LOW.

10