74LS195 View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

View to exact match

74LS195 Datasheet PDF : 6 Pages

| |||

SN54 / 74LS195A

DEFINITIONS OF TERMS

SETUP TIME(ts) —is defined as the minimum time required

for the correct logic level to be present at the logic input prior

to the clock transition from LOW to HIGH in order to be

recognized and transferred to the outputs.

HOLD TIME (th) — is defined as the minimum time following

the clock transition from LOW to HIGH that the logic level must

be maintained at the input in order to ensure continued

recognition. A negative HOLD TIME indicates that the correct

logic level may be released prior to the clock transition from

LOW to HIGH and still be recognized.

RECOVERY TIME (trec) — is defined as the minimum time

required between the end of the reset pulse and the clock

transition from LOW to HIGH in order to recognize and transfer

HIGH Data to the Q outputs.

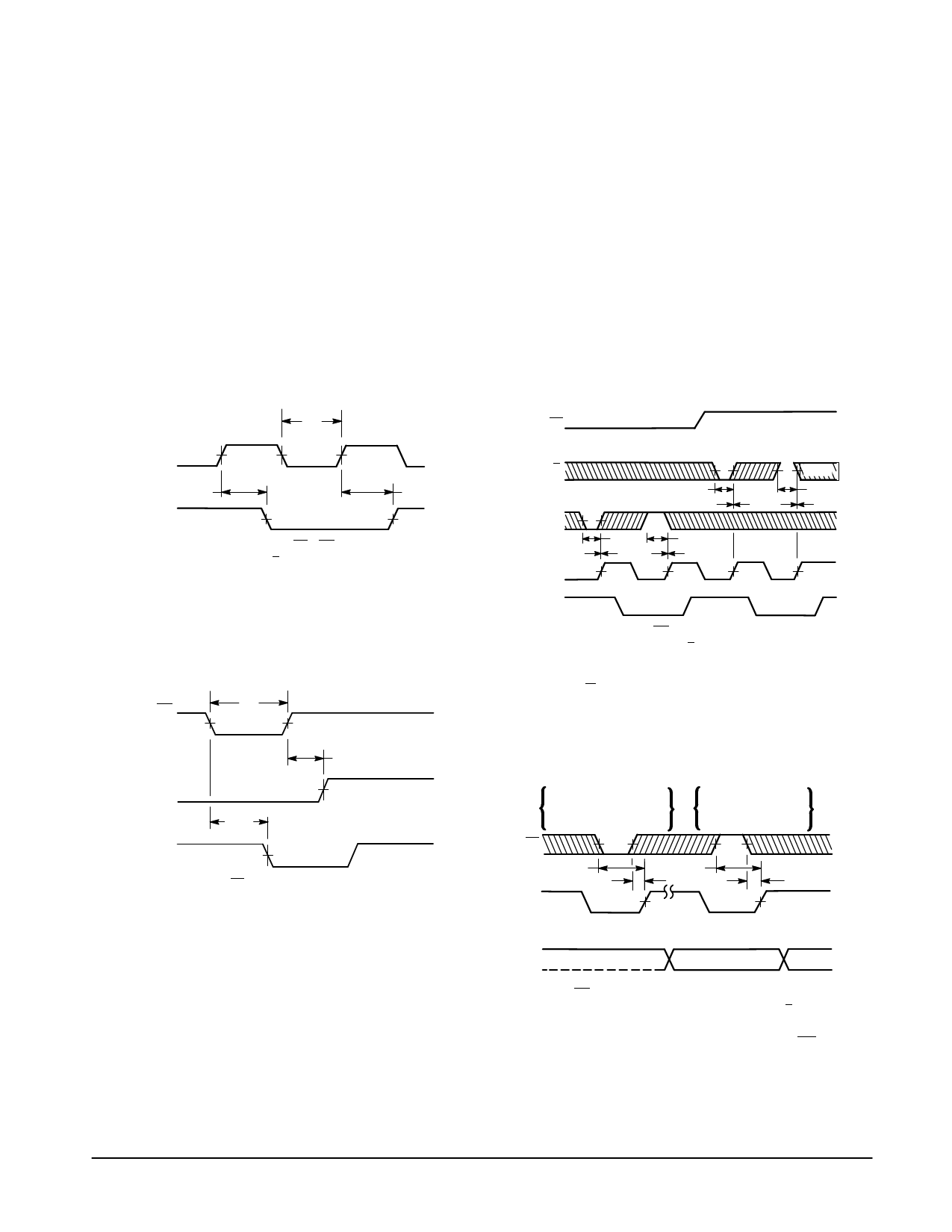

AC WAVEFORMS

The shaded areas indicate when the input is permitted to change for predictable output performance.

tW

1.3 V

CLOCK

tPHL

OUTPUT

1.3 V

1.3 V

tPLH

1.3 V

CONDITIONS: J = PE = MR = H

K=L

Figure 1. Clock to Output Delays and

Clock Pulse Width

MR

tW

1.3 V

1.3 V

CLOCK

OUTPUT

trec

1.3 V

tPHL

1.3 V

CONDITIONS: PE = L

PO = P1 = P2 = P3 = H

Figure 2. Master Reset Pulse Width, Master Reset

to Output Delay and Master Reset to Clock

Recovery Time

PE

J&K

ts(L)

th(L) = 0

P0 P1 P2 P3

ts(L)

th(L) = 0

CLOCK

ts(H)

th(H) = 0

1.3ĂV

OUTPUT*

1.3 V

ts(H)

th(H) = 0

1.3 V

CONDITIONS: MR = H

*J AND K SET-UP TIME AFFECTS Q0 ONLY

Figure 3. Setup (ts) and Hold (th) Time for Serial Data

(J & K) and Parallel Data (P0, P1, P2, P3)

LOAD PARALLEL DATA

LOAD SERIAL DATA

SHIFT RIGHT

PE

1.3 V

1.3 V

ts(L) trel

ts(H) trel

CLOCK

1.3 V

1.3 V

OUTPUT

Qn = Pn

Qn* = Qn-1

CONDITIONS: MR = H

*Q0 STATE WILL BE DETERMINED BY J AND K INPUTS .

Figure 4. Setup (ts) and Hold (th) Time for PE Input

FAST AND LS TTL DATA

5-369