IDT72510L25J View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

View to exact match

IDT72510L25J

IDT72510L25J Datasheet PDF : 32 Pages

| |||

IDT72510, IDT72520

BUS MATCHING BIDIRECTIONAL FIFO

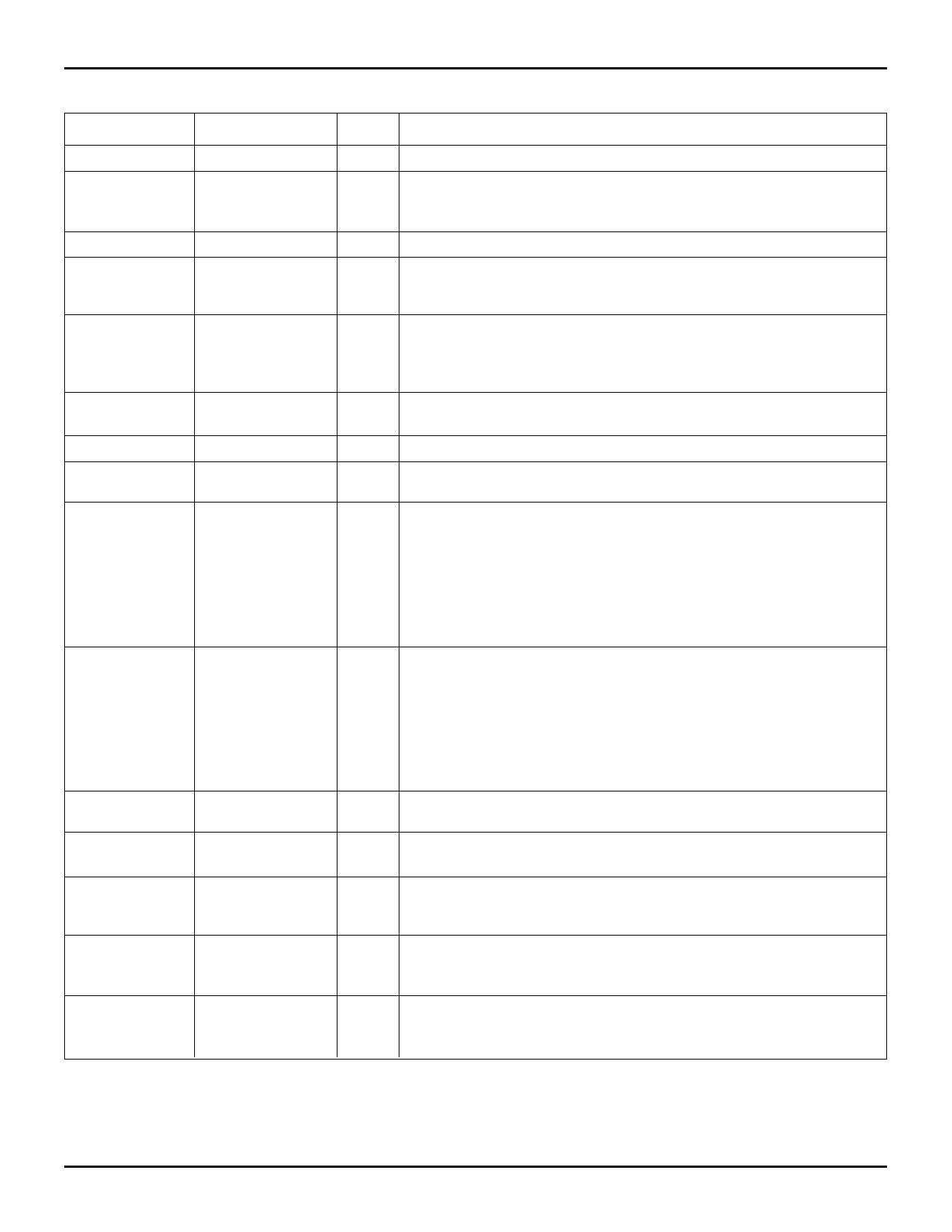

PIN DESCRIPTIONS

Symbol

DA0-DA15

DA16-DA17

Name

Data A

Parity A

CSA

Chip Select A

DSA

Data Strobe A

R/WA

Read/Write A

A0, A1

DB0-DB7

DB8

RB (DSB)

Addresses

Data B

Parity B

Read B

WB (R/WB)

Write B

RER

REW

LDRER

LDREW

REQ

Reread

Rewrite

Load Reread

Load Rewrite

Request

COMMERCIAL TEMPERATURE RANGE

I/O

I/O

I/O

I

I

I

I

I/O

I/O

I or O

I or O

I

I

I

I

I

Description

Data inputs and outputs for 16 bits of the 18-bit Port A bus.

DA16 is the parity bit for DA0-DA7. DA17 is the parity bit for DA8-

DA15. DA16 and DA17 can be used as two extra data bits if the

parity generate function is disabled.

Port A is accessed when Chip Select A is LOW.

Data is written into Port A on the rising edge of Data Strobe when

Chip Select is LOW. Data is read out of Port A on the falling edge of

Data Strobe when Chip Select is LOW.

This pin controls the read or write direction of Port A. When CSA is

LOW and R/WA is HIGH, data is read from Port A on the falling edge

of DSA. When CSA is LOW and R/WA is LOW, data is written into

Port A on the rising edge of DSA.

When Chip Select A is asserted, A0, A1, and Read/Write A are used

to select one of six internal resources.

Data inputs and outputs for 8 bits of the 9-bit Port B bus.

DB8 is the parity bit for DB0-DB7. DB8 can be used as a data bit if

the parity generate function is disabled.

If Port B is programmed to processor mode, this pin functions as an

input. If Port B is programmed to peripheral mode this pin functions

as an output. This pin can function as part of an Intel-style interface

(RB) or as part of a Motorola-style interface (DSB). As an Intel-style

interface, data is read from Port B on a falling edge of RB. As a

Motorola-style interface, data is read on the falling edge of DSB or

written on the rising edge of DSB through Port B. The Default is Intel-

style processor mode (RB as an input).

If Port B is programmed to processor mode, this pin functions as an

input. If Port B is programmed to peripheral mode this pin functions

as an output. This pin can function as part of an Intel-style interface

(WB) or as part of a Motorola-style interface (R/WB). As an Intel

style interface, data is written to Port B on a rising edge of WB. As

a Motorola-style interface, data is read (R/WB = HIGH) or written (R/

WB = LOW) to Port B in conjunction with a Data Strobe B falling or

rising edge. The Default is Intel-style processor mode (WB as input).

Loads A-to-B FIFO Read Pointer with the value of the Reread

Pointer when LOW.

Loads B-to-A FIFO Write Pointer with the value of the Rewrite

Pointer when LOW.

Loads the Reread Pointer with the value of the A-to-B FIFO Read

Pointer when HIGH. This signal is accessible through the Command

Register.

Loads the Rewrite Pointer with the value of the B-to-A FIFO Write

Pointer when HIGH. This signal is accessible through the Command

Register.

When Port B is programmed in peripheral mode, asserting this pin

begins a data transfer. Request can be programmed either active

HIGH or active LOW.

2669 tbl 01

5.31

3