VPC3211C View Datasheet(PDF) - Micronas

Part Name

Description

View to exact match

VPC3211C Datasheet PDF : 48 Pages

| |||

VPC 3205C, VPC 3215C

PRELIMINARY DATA SHEET

Video Processor Family

Release Note: Revision bars indicate significant

changes to the previous edition.

– I2C-Bus Interface

– one 20.25 MHz crystal, few external components

– 68-pin PLCC package

1. Introduction

The VPC 32x5 is a high-quality, single-chip video

front-end, which is targeted for 4:3 and 16:9, 50/60 and

100/120 Hz TV sets. It can be combined with other

members of the DIGIT3000 IC family (such as CIP

3250A, DDP 3300A, TPU 3040) and/or it can be used

with 3rd-party products.

The main features of the VPC 32x5 are

– all-digital video processing

– high-performance adaptive 4H comb filter Y/C sepa-

rator with adjustable vertical peaking

– multi-standard color decoder PAL/NTSC/SECAM

including all substandards

– 4 composite, 1 S-VHS input, 1 composite output

– integrated high-quality A/D converters and associ-

ated clamp and AGC circuits

– multi-standard sync processing

– linear horizontal scaling (0.25 ... 4), as well as

non-linear horizontal scaling ‘panorama vision’

– PAL+ preprocessing (VPC 3215)

– line-locked clock, data and sync output (VPC 3215)

– display/deflection control (VPC 3205)

– submicron CMOS technology

1.1. System Architecture

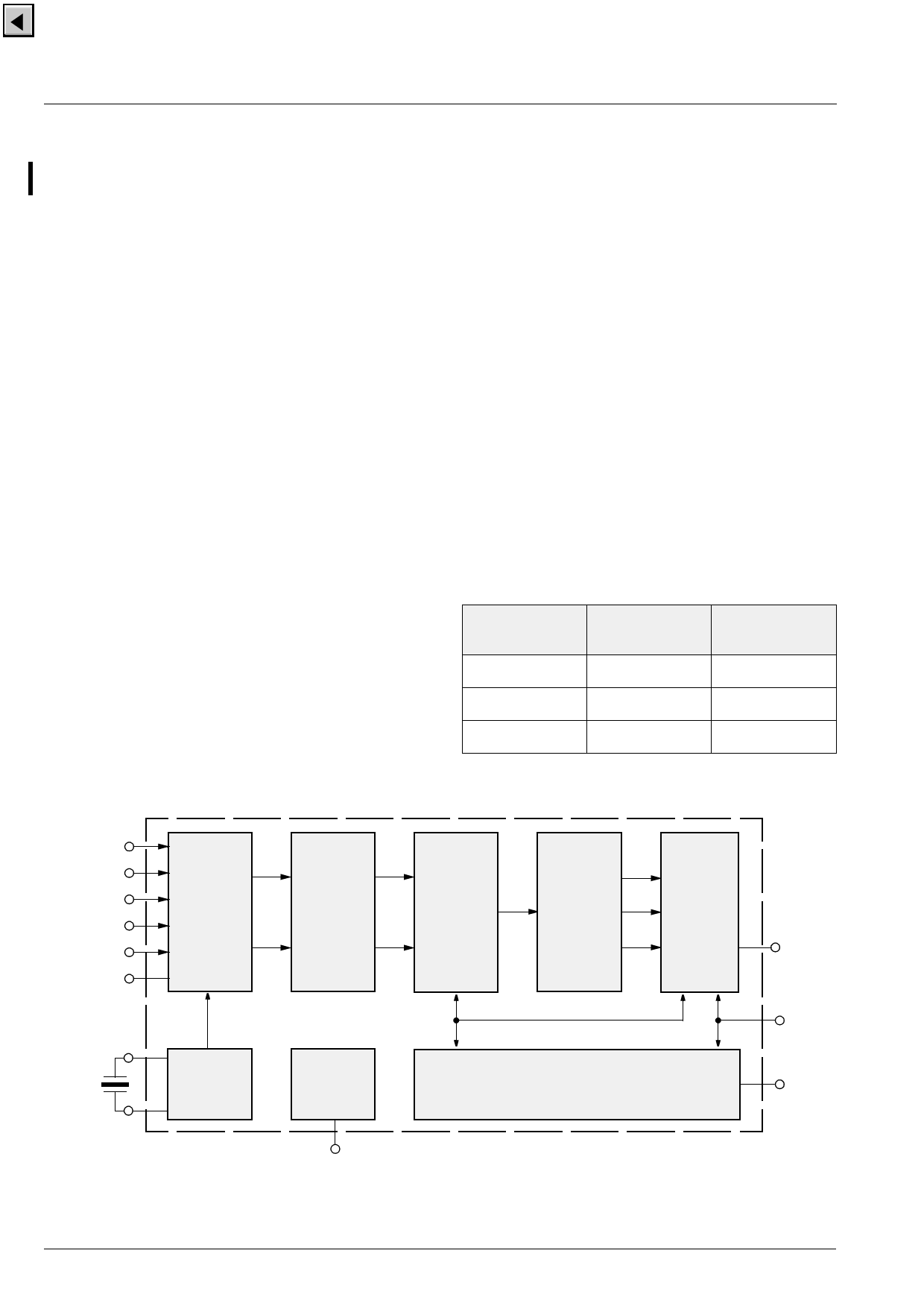

Fig. 1–1 shows the block diagram of the video proces-

sor.

1.2. Video Processor Family

The VPC video processor family supports 15/32 kHz

systems and is available with different comb filter

options. The 50 Hz/single scan versions provide con-

trolling for the display and the vertical/east west deflec-

tion of DDP 3300A. The 100 Hz/double scan versions

have a line-locked clock output interface and the

PAL+ preprocessing option. Table 1–1 gives an over-

view of the VPC video processor family.

Table 1–1: VPC Processor Family

Features

4H comb filter

2H comb filter

no comb filter

50 Hz/

single scan

VPC 3205C

VPC 3200A

VPC 3201A

100 Hz/

double scan

VPC 3215C

VPC 3210A

VPC 3211A

V1

V2/Y

C

V3

V4

CVBS

Out

Front-End

2*ADC,

8 bit

Adaptive

Combfilter

Clock Gen.

DCO

I2C

20.25

MHz

I2C

Fig. 1–1: VPC 32x5C block diagram

Color

Decoder

NTSC

PAL

SECAM

Horizontal

Scaler

Panorama

mode

Output

Formatter

Sync Processing

line-locked clock synthesis

YUV

clock

H/V

4

Micronas