Mosel Vitelic Corporation

V58C3643204SAT 数据手册 ( 数据表 ) - Mosel Vitelic Corporation

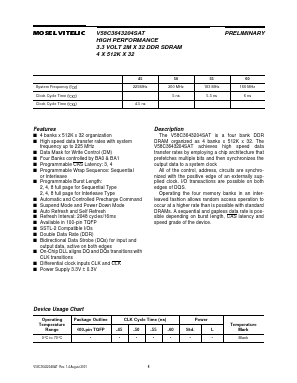

Description

The V58C3643204SAT is a four bank DDR DRAM organized as 4 banks x 512K x 32. The V58C3643204SAT achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock

FEATUREs

■ 4 banks x 512K x 32 organization

■ High speed data transfer rates with system frequency up to 225 MHz

■ Data Mask for Write Control (DM)

■ Four Banks controlled by BA0 & BA1

■ Programmable CAS Latency: 3, 4

■ Programmable Wrap Sequence: Sequential or Interleave

■ Programmable Burst Length:

2, 4, 8 full page for Sequential Type

2, 4, 8 full page for Interleave Type

■ Automatic and Controlled Precharge Command

■ Suspend Mode and Power Down Mode

■ Auto Refresh and Self Refresh

■ Refresh Interval: 2048 cycles/16ms

■ Available in 100-pin TQFP

■ SSTL-2 Compatible I/Os

■ Double Data Rate (DDR)

■ Bidirectional Data Strobe (DQs) for input and output data, active on both edges

■ On-Chip DLL aligns DQ and DQs transitions with CLK transitions

■ Differential clock inputs CLK and CLK

■ Power Supply 3.3V ± 0.3V