Toshiba

TC581282A 数据手册 ( 数据表 ) - Toshiba

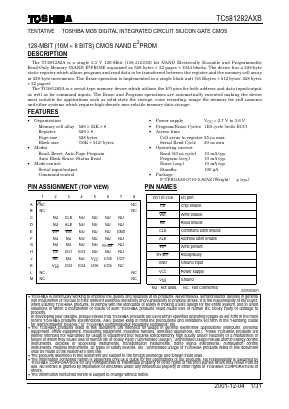

128-MBIT (16M × 8 BITS) CMOS NAND E2PROM

DESCRIPTION

The TC581282A is a single 3.3 V 128-Mbit (138,412,032) bit NAND Electrically Erasable and Programmable Read-Only Memory (NAND E2PROM) organized as 528 bytes × 32 pages × 1024 blocks. The device has a 528-byte static register which allows program and read data to be transferred between the register and the memory cell array in 528-byte increments. The Erase operation is implemented in a single block unit (16 Kbytes + 512 bytes: 528 bytes × 32 pages).

FEATURES

• Organization

Memory cell allay 528 × 32K × 8

Register 528 × 8

Page size 528 bytes

Block size (16K + 512) bytes

• Modes

Read, Reset, Auto Page Program

Auto Block Erase, Status Read

• Mode control

Serial input/output

Command control

• Power supply VCC = 2.7 V to 3.6 V

• Program/Erase Cycles 1E5 cycle (with ECC)

• Access time

Cell array to register 25 µs max

Serial Read Cycle 50 ns min

• Operating current

Read (50 ns cycle) 10 mA typ.

Program (avg.) 10 mA typ.

Erase (avg.) 10 mA typ.

Standby 100 µA

• Package

P-TFBGA56-0710-0.80AZ (Weight: g typ.)