Silicon Storage Technology

SST49LF004C-33-4C-NH 数据手册 ( 数据表 ) - Silicon Storage Technology

PRODUCT DESCRIPTION

The SST49LF00xC flash memory devices are designed to interface with host controllers (chipsets) that support a low pin-count (LPC) interface for system firmware applications. The SST49LF00xC device complies with Intel’s LPC Interface Specification 1.1, supporting a Burst-Read (up to 128 bytes in a single operation) which enables a 15.6 MByte per second data transfer. The LPC interface operates with 5 signal pins versus 28 pins of a 8-bit parallel flash memory. This frees up pins on the ASIC host controller resulting in lower ASIC costs and a reduction in overall system costs due to simplified signal routing.

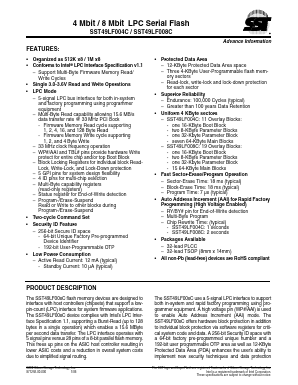

FEATURES:

• Organized as 512K x8 / 1M x8

• Conforms to Intel® LPC Interface Specification v1.1

– Support Multi-Byte Firmware Memory Read/ Write Cycles

• Single 3.0-3.6V Read and Write Operations

• LPC Mode

– 5-signal LPC bus interface for both in-system and factory programming using programmer equipment

– Multi-Byte Read capability allowing 15.6 MB/s data transfer rate @ 33 MHz PCI clock

- Firmware Memory Read cycle supporting 1, 2, 4, 16, and 128 Byte Read

- Firmware Memory Write cycle supporting 1, 2, and 4 Byte Write

– 33 MHz clock frequency operation

– WP#/AAI and TBL# pins provide hardware Write protect for entire chip and/or top Boot Block

– Block Locking Registers for individual block Read Lock, Write-Lock, and Lock-Down protection

– 5 GPI pins for system design flexibility

– 4 ID pins for multi-chip selection

– Multi-Byte capability registers (read-only registers)

– Status register for End-of-Write detection

– Program-/Erase-Suspend Read or Write to other blocks during Program-/Erase-Suspend

• Two-cycle Command Set

• Security ID Feature

– 256-bit Secure ID space

- 64-bit Unique Factory Pre-programmed Device Identifier

- 192-bit User-Programmable OTP

• Low Power Consumption

– Active Read Current: 12 mA (typical)

- Standby Current: 10 µA (typical)

• Protected Data Area

– 12-KByte Protected Data Area space

– Three 4-KByte User-Programmable flash memory sectors

– Read-lock, write-lock and lock-down protection for each sector

• Superior Reliability

– Endurance: 100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Uniform 4 KByte sectors

– SST49LF004C: 11 Overlay Blocks:

- one 16-KByte Boot Block

- two 8-KByte Parameter Blocks

- one 32-Kbyte Parameter Block

- seven 64-KByte Main Blocks

– SST49LF008C: 19 Overlay Blocks:

- one 16-KByte Boot Block

- two 8-KByte Parameter Blocks

- one 32-Kbyte Parameter Block

- 15 64-KByte Main Blocks

• Fast Sector-Erase/Program Operation

– Sector-Erase Time: 18 ms (typical)

– Block-Erase Time: 18 ms (typical)

– Program Time: 7 µs (typical)

• Auto Address Increment (AAI) for Rapid Factory Programming (High Voltage Enabled)

– RY/BY# pin for End-of-Write detection

– Multi-Byte Program

– Chip Rewrite Time: (typical)

- SST49LF004C: 1 seconds

- SST49LF008C: 2 seconds

• Packages Available

– 32-lead PLCC

– 32-lead TSOP (8mm x 14mm)

• All non-Pb (lead-free) devices are RoHS compliant