PMC-Sierra

PM7329(2001) 数据手册 ( 数据表 ) - PMC-Sierra

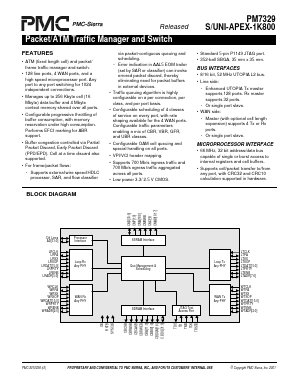

FEATURES

• ATM (fixed length cell) and packet/frame traffic manager and switch.

• 128 line ports, 4 WAN ports, and a high speed microprocessor port. Any port to any port switching for 1024 independent connections.

• Manages up to 256 Kbyte cell (16 Mbyte) data buffer and 4 Mbyte context memory shared over all ports.

• Configurable progressive throttling of buffer consumption, with memory reservation under high consumption. Performs EFCI marking for ABR support.

• Buffer congestion controlled via Partial Packet Discard, Early Packet Discard (PPD/EPD). Cell at a time discard also supported.

• For frame/packet flows:

• Supports external wire speed HDLC processor, SAR, and flow classifier via packet-contiguous queuing and scheduling.

• Error indication in AAL5 EOM trailer (set by SAR or classifier) can invoke errored packet discard, thereby eliminating need for packet buffers in external devices.

• Traffic queuing algorithm is highly configurable on a per connection, per class, and per port basis.

• Configurable scheduling of 4 classes of service on every port, with rate shaping available for the 4 WAN ports. Configurable traffic parameters enabling a mix of CBR, VBR, GFR, and UBR classes.

• Configurable OAM cell queuing and special handling on all ports.

• VPI/VCI header mapping.

• Supports 700 Mb/s ingress traffic and 700 Mb/s egress traffic aggregated across all ports.

• Low power 3.3/ 2.5 V CMOS.

• Standard 5-pin P1149 JTAG port.

• 352-ball SBGA, 35 mm x 35 mm.

APPLICATIONS

• Mini Digital Subscriber Loop Access Multiplexer (mini-DSLAM).

• Subscriber Access equipment.

• Digital Loop Card traffic aggregation.