PMC-Sierra

PM535149 数据手册 ( 数据表 ) - PMC-Sierra

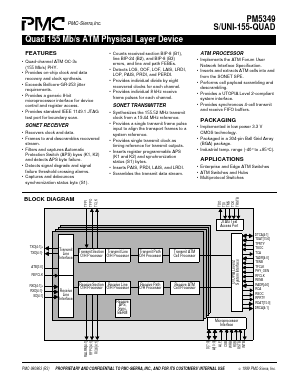

FEATURES

• Quad-channel ATM OC-3c (155 Mb/s) PHY.

• Provides on-chip clock and data recovery and clock synthesis.

• Exceeds Bellcore-GR-253 jitter requirements.

• Provides a generic 8-bit microprocessor interface for device control and register access.

• Provides standard IEEE 1149.1 JTAG test port for boundary scan.

SONET RECEIVER

• Recovers clock and data.

• Frames to and descrambles recovered stream.

• Filters and captures Automatic Protection Switch (APS) byes (K1, K2) and detects APS byte failure.

• Detects signal degrade and signal failure threshold crossing alarms.

• Captures and debounces synchronization status byte (S1).

• Counts received section BIP-8 (B1), line BIP-24 (B2), and BIP-8 (B3) errors, and line and path FEBEs.

• Detects LOS, OOF, LOF, LAIS, LRDI, LOP, PAIS, PRDI, and PERDI.

• Provides individual divide by eight recovered clocks for each channel.

• Provides individual 8 kHz receive frame pulses for each channel.

SONET TRANSMITTER

• Synthesizes the 155.52 MHz transmit clock from a 19.44 MHz reference.

• Provides a single transmit frame pulse input to align the transport frames to a system reference.

• Provides single transmit clock as timing reference for transmit outputs.

• Inserts register programmable APS (K1 and K2) and synchronization status (S1) bytes.

• Inserts PAIS, PRDI, LAIS, and LRDI.

• Scrambles the transmit data stream.

ATM PROCESSOR

• Implements the ATM Forum User Network Interface Specification.

• Inserts and extracts ATM cells into and from the SONET SPE.

• Performs cell payload scrambling and descrambling.

• Provides a UTOPIA Level 2-compliant system interface.

• Provides synchronous 4-cell transmit and receive FIFO buffers.

PACKAGING

• Implemented in low power 3.3 V CMOS technology.

• Packaged in a 304-pin Ball Grid Array (BGA) package.

• Industrial temp. range (-40° to +85°C).

APPLICATIONS

• Enterprise and Edge ATM Switches

• ATM Switches and Hubs

• Multiprotocol Switches