Zarlink Semiconductor Inc

MT90401AB 数据手册 ( 数据表 ) - Zarlink Semiconductor Inc

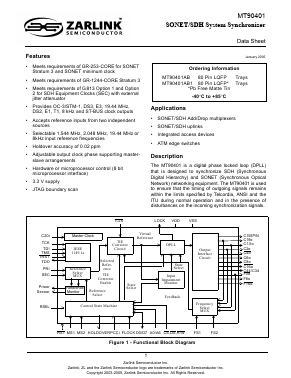

Description

The MT90401 is a digital phase locked loop (DPLL) that is designed to synchronize SDH (Synchronous Digital Hierarchy) and SONET (Synchronous Optical Network) networking equipment. The MT90401 is used to ensure that the timing of outgoing signals remains within the limits specified by Telcordia, ANSI and the ITU during normal operation and in the presence of disturbances on the incoming synchronization signals.

FEATUREs

• Meets requirements of GR-253-CORE for SONET Stratum 3 and SONET minimum clock

• Meets requirements of GR-1244-CORE Stratum 3

• Meets requirements of G.813 Option 1 and Option 2 for SDH Equipment Clocks (SEC) with external jitter attenuator

• Provides OC-3/STM-1, DS3, E3, 19.44 MHz, DS2, E1, T1, 8 kHz and ST-BUS clock outputs

• Accepts reference inputs from two independent sources

• Selectable 1.544 MHz, 2.048 MHz, 19.44 MHz or 8kHz input reference frequencies

• Holdover accuracy of 0.02 ppm

• Adjustable output clock phase supporting master-slave arrangements

• Hardware or microprocessor control (8 bit microprocessor interface)

• 3.3 V supply

• JTAG boundary scan

APPLICATIONs

• SONET/SDH Add/Drop multiplexers

• SONET/SDH uplinks

• Integrated access devices

• ATM edge switches