Micron Technology

MT46V16M8TG-6 数据手册 ( 数据表 ) - Micron Technology

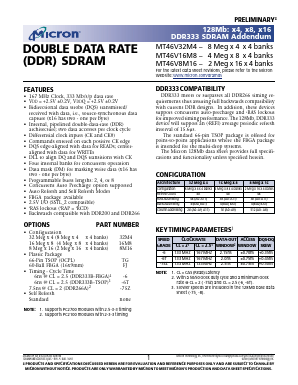

DDR333 COMPATIBILITY

DDR333 meets or surpasses all DDR266 timing requirements thus assuring full backwards compatibility with current DDR designs. In addition, these devices support concurrent auto-precharge and tRAS lockout for improved timing performance. The 128Mb, DDR333 device will support an (tREFI) average periodic refresh interval of 15.6µs.

The standard 66-pin TSOP package is offered for point-to-point applications where the FBGA package is intended for the multi-drop systems. The Micron 128Mb data sheet provides full specifications and functionality unless specified herein.

FEATURES

• 167 MHz Clock, 333 Mb/s/p data rate

• VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V

• Bidirectional data strobe (DQS) transmitted/received with data, i.e., source-synchronous data capture (x16 has two - one per byte)

• Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

• Differential clock inputs (CK and CK#)

• Commands entered on each positive CK edge

• DQS edge-aligned with data for READs; center aligned with data for WRITEs

• DLL to align DQ and DQS transitions with CK

• Four internal banks for concurrent operation

• Data mask (DM) for masking write data (x16 has two - one per byte)

• Programmable burst lengths: 2, 4, or 8

• Concurrent Auto Precharge option supported

• Auto Refresh and Self Refresh Modes

• FBGA package available

• 2.5V I/O (SSTL_2 compatible)

• tRAS lockout (tRAP = tRCD)

• Backwards compatible with DDR200 and DDR266