Micron Technology

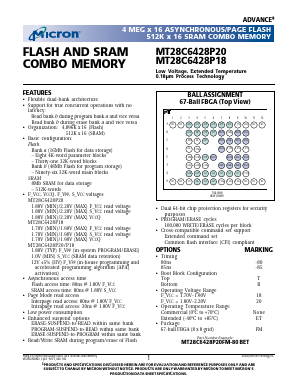

MT28C6428P18 数据手册 ( 数据表 ) - Micron Technology

GENERAL DESCRIPTION

The MT28C6428P20 and MT28C6428P18 combination Flash and SRAM memory devices provide a compact, low-power solution for systems where PCB real estate is at a premium. The dual-bank Flash devices are high-performance, high-density, nonvolatile memory with a revolutionary architecture that can significantly improve system performance.

FEATURES

• Flexible dual-bank architecture

• Support for true concurrent operations with no latency:

Read bank b during program bank a and vice versa

Read bank b during erase bank a and vice versa

• Organization: 4,096K x 16 (Flash)

512K x 16 (SRAM)

• Basic configuration:

Flash

Bank a (16Mb Flash for data storage)

– Eight 4K-word parameter blocks

– Thirty-one 32K-word blocks

Bank b (48Mb Flash for program storage)

– Ninety-six 32K-word main blocks

SRAM

8Mb SRAM for data storage

– 512K-words

• F_VCC, VCCQ, F_VPP, S_VCC voltages

MT28C6428P20

1.80V (MIN)/2.20V (MAX) F_VCC read voltage

1.80V (MIN)/2.20V (MAX) S_VCC read voltage

1.80V (MIN)/2.20V (MAX) VCCQ

MT28C6428P18

1.70V (MIN)/1.90V (MAX) F_VCC read voltage

1.70V (MIN)/1.90V (MAX) S_VCC read voltage

1.70V (MIN)/1.90V (MAX) VCCQ

MT28C6428P20/P18

1.80V (TYP) F_VPP (in-system PROGRAM/ERASE)

1.0V (MIN) S_VCC (SRAM data retention)

12V ±5% (HV) F_VPP (in-house programming and

accelerated programming algorithm [APA]

activation)

• Asynchronous access time

Flash access time: 80ns @ 1.80V F_VCC

SRAM access time: 80ns @ 1.80V S_VCC

• Page Mode read access

Interpage read access: 80ns @ 1.80V F_VCC

Intrapage read access: 30ns @ 1.80V F_VCC

• Low power consumption

• Enhanced suspend options

ERASE-SUSPEND-to-READ within same bank

PROGRAM-SUSPEND-to-READ within same bank

ERASE-SUSPEND-to-PROGRAM within same bank

• Read/Write SRAM during program/erase of Flash

• Dual 64-bit chip protection registers for security purposes

• PROGRAM/ERASE cycles

100,000 WRITE/ERASE cycles per block

• Cross-compatible command set support

Extended command set

Common flash interface (CFI) compliant