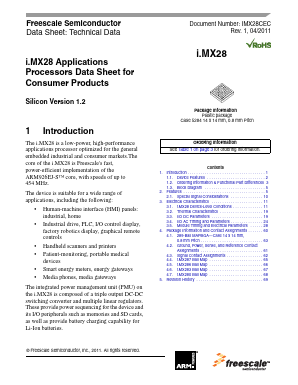

Freescale Semiconductor

MCIMX280CVM4B 数据手册 ( 数据表 ) - Freescale Semiconductor

Introduction

The i.MX28 is a low-power, high-performance applications processor optimized for the general embedded industrial and consumer markets.The core of the i.MX28 is Freescales fast, power-efficient implementation of the ARM926EJ-S™ core, with speeds of up to 454 MHz.

The device is suitable for a wide range of applications, including the following:

• Human-machine interface (HMI) panels:

industrial, home

• Industrial drive, PLC, I/O control display,

factory robotics display, graphical remote

controls

• Handheld scanners and printers

• Patient-monitoring, portable medical

devices

• Smart energy meters, energy gateways

• Media phones, media gateways

The integrated power management unit (PMU) on the i.MX28 is composed of a triple output DC-DC switching converter and multiple linear regulators. These provide power sequencing for the device and its I/O peripherals such as memories and SD cards, as well as provide battery charging capability for Li-Ion batteries.

Device Features

The following lists the features of the i.MX28:

• ARM926EJ-S CPU running at 454 MHz:

— 16-Kbyte instruction cache and 32-Kbyte data cache

— ARM embedded trace macrocell (CoreSight™ ETM9™)

— Parallel JTAG interface

• 128 KBytes of integrated low-power on-chip SRAM

• 128 KBytes of integrated mask-programmable on-chip ROM

• 1280 bits of on-chip one-time-programmable (OCOTP) ROM

• 16-bit mobile DDR (mDDR) (1.8 V), DDR2 (1.8 V) and LV-DDR2 (1.5 V), up to 205 MHz DDR

clock frequency with voltage overdrive

• Support for up to eight NAND flash memory devices with up to 20-bit BCH ECC

• Four synchronous serial ports (SSP) for SDIO/MMC/MS/SPI. Two can be used for

SDIO/MMC/MS interfaces (supports SD2.0, eMMC4.4 and MSPro), and all can be used for the

SPI interface.

• 10/100-Mbps Ethernet MAC compatible with IEEE Std 802.3™, supporting

IEEE Std 1588™-compatible hardware timestamp. Also supports 50-MHz/25-MHz clock output

for external Ethernet PHY.

• Two 2.0B protocol-compatible Controller Area Network (CAN) interfaces

• One USB2.0 OTG device/host controller and PHY

• One USB2.0 host controller and PHY

• LCD controller, up to 24-bit RGB (DOTCK) modes and 24-bit system-mode

• Pixel-processing pipeline (PXP) supports full path from color-space conversion, scaling,

alpha-blending to rotation without intermediate memory access.

• SPDIF transmitter

• Dual serial audio interface (SAIF) to support full-duplex transmit and receive operations; each

SAIF supports three stereo pairs

• Five application Universal Asynchronous Receiver-Transmitters (UARTs), up to 3.25 Mbps with

hardware flow control

• One debug UART operating at up to 115 Kb/s using programmed I/O

• Two I2C master/slave interfaces, up to 400 kbps

• Four 32-bit timers and a rotary decoder

• Eight Pulse Width Modulators (PWMs)

• Real-time clock (RTC)

• GPIO with interrupt capability

• Power Management Unit (PMU) supports a triple output DC-DC switching converter, multiple

linear regulators, battery charger, and detector.

• 16-channel Low-Resolution A/D Converter (LRADC)

• 4/5-wire touchscreen controller

• Up to 8X8 keypad matrix with button-detect circuit

• Single channel High Speed A/D Converter (HSADC), up to 2 Msps data rate

• Security features:

— Read-only unique ID for Digital Rights Management (DRM) algorithms

— Secure boot using 128-bit AES hardware decryption

— SHA-1 and SHA256 hashing hardware

— High assurance boot (HAB4)

• Offered in 289-pin Ball Grid Array (BGA)