MITSUBISHI ELECTRIC

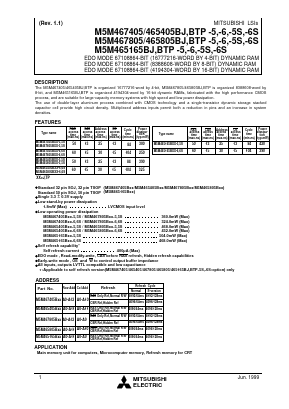

M5M465165BJ-5 数据手册 ( 数据表 ) - MITSUBISHI ELECTRIC

DESCRIPTION

The M5M467405/465405BJ,BTP is organized 16777216-word by 4-bit, M5M467805/465805BJ,BTP is organized 8388608-word by 8-bit, and M5M465165BJ,BTP is organized 4194304-word by 16-bit dynamic RAMs, fabricated with the high performance CMOS process, and are suitable for large-capacity memory systems with high speed and low power dissipation.

The use of double-layer aluminum process combined with CMOS technology and a single-transistor dynamic storage stacked capacitor cell provide high circuit density. Multiplexed address inputs permit both a reduction in pins and an increase in system densities.

FEATURES

• Standard 32 pin SOJ, 32 pin TSOP (M5M467405Bxx/M5M465405Bxx/M5M467805Bxx/M5M465805Bxx)

Standard 50 pin SOJ, 50 pin TSOP (M5M465165Bxx)

• Single 3.3 ± 0.3V supply

• Low stand-by power dissipation

1.8mW (Max) LVCMOS input level

• Low operating power dissipation

M5M467405Bxx-5,5S / M5M467805Bxx-5,5S 360.0mW (Max)

M5M467405Bxx-6,6S / M5M467805Bxx-6,6S 324.0mW (Max)

M5M465405Bxx-5,5S / M5M465805Bxx-5,5S 468.0mW (Max)

M5M465405Bxx-6,6S / M5M465805Bxx-6,6S 432.0mW (Max)

M5M465165Bxx-5,5S 504.0mW (Max)

M5M465165Bxx-6,6S 468.0mW (Max)

• Self refresh capability*

Self refresh current 400µA (Max)

• EDO mode , Read-modify-write, CAS before RAS refresh, Hidden refresh capabilities

• Early-write mode , OE and W to control output buffer impedance

• All inputs, outputs LVTTL compatible and low capacitance