MITSUBISHI ELECTRIC

M5M417400CJ-7 数据手册 ( 数据表 ) - MITSUBISHI ELECTRIC

DESCRIPTION

This is a family of 4194304-word by 4-bit dynamic RAMS, fabricated with the high performance CMOS process, and is ideal for large-capacity memory systems where high speed, low power dissipation, and low costs are essential.

The use of double-layer metal process combined with twin-well CMOS technology and a single-transistor dynamic storage stacked capacitor cell provide high circuit density at reduced costs. Multiplexed address inputs permit both a reduction in pins and an increase in system densities.

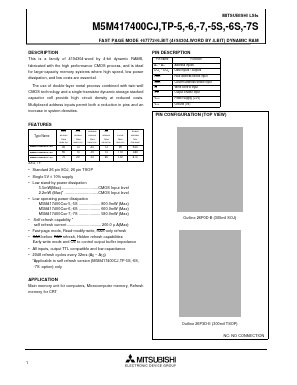

FEATURES

• Standard 26 pin SOJ, 26 pin TSOP

• Single 5V ± 10% supply

• Low stand-by power dissipation

5.5mW(Max)..................................CMOS Input level

2.2mW (Max)* ...............................CMOS Input level

• Low operating power dissipation

M5M417400Cxx-5,-5S .................... 800.0mW (Max)

M5M417400Cxx-6,-6S .................... 660.0mW (Max)

M5M417400Cxx-7,-7S .................... 580.0mW (Max)

• Self refresh capability *

self refresh current ................................ 200.0 µ A(Max)

• Fast-page mode, Read-modify-write, RAS-only refresh

• CAS before RAS refresh, Hidden refresh capabilities Early-write mode and OE to control output buffer impedance

• All inputs, output TTL compatible and low capacitance

• 2048 refresh cycles every 32ms (A0 ~ A10)

*Applicable to self refresh version (M5M417400CJ,TP-5S,-6S,-7S :option) only

APPLICATION

Main memory unit for computers, Microcomputer memory, Refresh memory for CRT