Sharp Electronics

LH540225 数据手册 ( 数据表 ) - Sharp Electronics

FUNCTIONAL DESCRIPTION

NOTE: Throughout this data sheet, a BOLD ITALIC type font is used for all references to Enhanced Operating Mode features which do not function in IDT-Compatible Operating Mode; and also for all references to the retransmit facility (which is not an IDT72215B/25B FIFO feature), even though it may be used – subject to some restrictions – in either of these two operating modes. Thus, readers interested only in using the LH540215/25 FIFOs in IDT-Compatible Operating Mode may skip over BOLD ITALIC sections, if they wish.

FEATURES

• Fast Cycle Times: 20/25/35 ns

• Pin-Compatible Drop-In Replacements for IDT72215B/25B FIFOs

• Choice of IDT-Compatible or Enhanced Operating Mode; Selected by an Input Control Signal

• Device Comes Up into One of Two Known Default States at Reset Depending on the State of the EMODE Control Input: Programming is Allowed, but is not Required

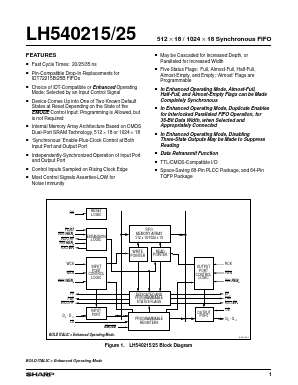

• Internal Memory Array Architecture Based on CMOS Dual-Port SRAM Technology, 512 × 18 or 1024 × 18

• ‘Synchronous’ Enable-Plus-Clock Control at Both Input Port and Output Port

• Independently-Synchronized Operation of Input Port and Output Port

• Control Inputs Sampled on Rising Clock Edge

• Most Control Signals Assertive-LOW for Noise Immunity

• May be Cascaded for Increased Depth, or Paralleled for Increased Width

• Five Status Flags: Full, Almost-Full, Half-Full, Almost-Empty, and Empty; ‘Almost’ Flags are Programmable

• In Enhanced Operating Mode, Almost-Full, Half-Full, and Almost-Empty Flags can be Made Completely Synchronous

• In Enhanced Operating Mode, Duplicate Enables for Interlocked Paralleled FIFO Operation, for 36-Bit Data Width, when Selected and Appropriately Connected

• In Enhanced Operating Mode, Disabling Three-State Outputs May be Made to Suppress Reading

• Data Retransmit Function

• TTL/CMOS-Compatible I/O

• Space-Saving 68-Pin PLCC Package, and 64-Pin TQFP Package