Lattice Semiconductor

ISPPAC-CLK5320S-01T64I 数据手册 ( 数据表 ) - Lattice Semiconductor

General Description

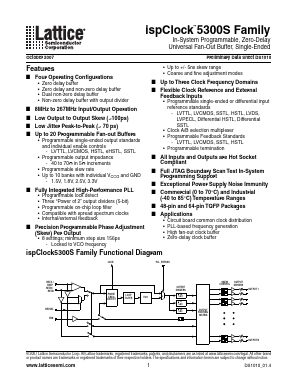

The ispClock5300S is an in-system-programmable zero delay universal fan-out buffer for use in clock distribution applications. The ispClock5312S, the first member of the ispClock5300S family, provides up to 12 single-ended ultra low skew outputs. Each pair of outputs may be independently configured to support separate I/O standards (LVTTL, LVCMOS -3.3V, 2.5V, 1.8, SSTL, HSTL) and output frequency. In addition, each output provides independent programmable control of termination, slew-rate, and timing skew. All configuration information is stored on-chip in non-volatile E2CMOS® memory.

FEATUREs

■ Four Operating Configurations

• Zero delay buffer

• Zero delay and non-zero delay buffer

• Dual non-zero delay buffer

• Non-zero delay buffer with output divider

■ 8MHz to 267MHz Input/Output Operation

■ Low Output to Output Skew (<100ps)

■ Low Jitter Peak-to-Peak (< 70 ps)

■ Up to 20 Programmable Fan-out Buffers

• Programmable single-ended output standards and individual enable controls

- LVTTL, LVCMOS, HSTL, eHSTL, SSTL

• Programmable output impedance

- 40 to 70Ω in 5Ω increments

• Programmable slew rate

• Up to 10 banks with individual VCCO and GND

- 1.5V, 1.8V, 2.5V, 3.3V

■ Fully Integrated High-Performance PLL

• Programmable lock detect

• Three “Power of 2” output dividers (5-bit)

• Programmable on-chip loop filter

• Compatible with spread spectrum clocks

• Internal/external feedback

■ Precision Programmable Phase Adjustment (Skew) Per Output

• 8 settings; minimum step size 156ps

- Locked to VCO frequency

• Up to +/- 5ns skew range

• Coarse and fine adjustment modes

■ Up to Three Clock Frequency Domains

■ Flexible Clock Reference and External Feedback Inputs

• Programmable single-ended or differential input reference standards

- LVTTL, LVCMOS, SSTL, HSTL, LVDS, LVPECL, Differential HSTL, Differential SSTL

• Clock A/B selection multiplexer

• Programmable Feedback Standards

- LVTTL, LVCMOS, SSTL, HSTL

• Programmable termination

■ All Inputs and Outputs are Hot Socket Compliant

■ Full JTAG Boundary Scan Test In-System Programming Support

■ Exceptional Power Supply Noise Immunity

■ Commercial (0 to 70°C) and Industrial (-40 to 85°C) Temperature Ranges

■ 48-pin and 64-pin TQFP Packages

■ Applications

• Circuit board common clock distribution

• PLL-based frequency generation

• High fan-out clock buffer

• Zero-delay clock buffer