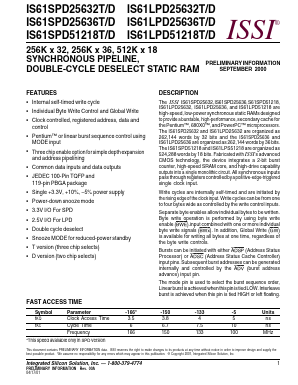

Integrated Silicon Solution

IS61SPD25636D 数据手册 ( 数据表 ) - Integrated Silicon Solution

DESCRIPTION

The ISSI IS61SPD25632, IS61SPD25636, S61SPD51218, IS61LPD25632, IS61LPD25636, and IS61LPD51218 are high-speed, low-power synchronous static RAMs designed to provide a burstable, high-performance, secondary cache for the Pentium™, 680X0™, and PowerPC™ microprocessors. The IS61SPD25632 and IS61LPD25632 are organized as 262,144 words by 32 bits and the IS61SPD25636 and IS61LPD25636 are organized as 262,144 words by 36 bits. The IS61SPD51218 and IS61LPS51218 are organized as 524,288 words by 18 bits. Fabricated with ISSIs advanced CMOS technology, the device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit. All synchronous inputs pass through registers controlledby a positive-edge-triggered single clock input.

FEATURES

• Internal self-timed write cycle

• Individual Byte Write Control and Global Write

• Clock controlled, registered address, data and control

• Pentium™ or linear burst sequence control using MODE input

• Three chip enable option for simple depth expansion and address pipelining

• Common data inputs and data outputs

• JEDEC 100-Pin TQFP and 119-pin PBGA package

• Single +3.3V, +10%, –5% power supply

• Power-down snooze mode

• 3.3V I/O For SPD

• 2.5V I/O For LPD

• Double cycle deselect

• Snooze MODE for reduced-power standby

• T version (three chip selects)

• D version (two chip selects)