Integrated Device Technology

IDT74SSTUBF32869A 数据手册 ( 数据表 ) - Integrated Device Technology

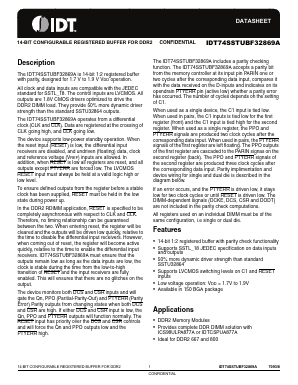

Description

The IDT74SSTUBF32869A is 14-bit 1:2 registered buffer with parity, designed for 1.7 V to 1.9 V VDD operation.

All clock and data inputs are compatible with the JEDEC standard for SSTL_18. The control inputs are LVCMOS. All outputs are 1.8V CMOS drivers optimized to drive the DDR2 DIMM load. They provide 50% more dynamic driver strength than the standard SSTU32864 outputs.

FEATUREs

• 14-bit 1:2 registered buffer with parity check functionality

• Supports SSTL_18 JEDEC specification on data inputs and outputs

• 50% more dynamic driver strength than standard SSTU32864

• Supports LVCMOS switching levels on C1 and RESET inputs

• Low voltage operation: VDD = 1.7V to 1.9V

• Available in 150 BGA package

APPLICATIONs

• DDR2 Memory Modules

• Provides complete DDR DIMM solution with ICS98ULPA877A or IDTCSPUA877A

• Ideal for DDR2 667 and 800