Integrated Circuit Systems

ICS9112BM-18 数据手册 ( 数据表 ) - Integrated Circuit Systems

Description

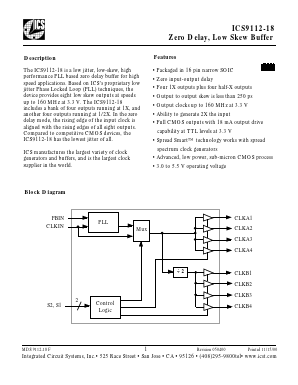

The ICS9112-18 is a low jitter, low-skew, high performance PLL based zero delay buffer for high speed applications. Based on ICS’s proprietary low jitter Phase Locked Loop (PLL) techniques, the device provides eight low skew outputs at speeds up to 160 MHz at 3.3 V. The ICS9112-18 includes a bank of four outputs running at 1X, and another four outputs running at 1/2X. In the zero delay mode, the rising edge of the input clock is aligned with the rising edges of all eight outputs. Compared to competitive CMOS devices, the ICS9112-18 has the lowest jitter of all.

ICS manufactures the largest variety of clock generators and buffers, and is the largest clock supplier in the world.

FEATUREs

• Packaged in 16 pin narrow SOIC

• Zero input-output delay

• Four 1X outputs plus four half-X outputs

• Output to output skew is less than 250 ps

• Output clocks up to 160 MHz at 3.3 V

• Ability to generate 2X the input

• Full CMOS outputs with 18 mA output drive

capability at TTL levels at 3.3 V

• Spread Smart™ technology works with spread

spectrum clock generators

• Advanced, low power, sub-micron CMOS process

• 3.0 to 5.5 V operating voltage