Siemens AG

HYB3164160AT 数据手册 ( 数据表 ) - Siemens AG

This device is a 64 MBit dynamic RAM organized 4 194 304 by 16 bits. The device is fabricated on an advanced second generation 64Mbit 0,35µm-CMOS silicon gate process technology. The circuit and process design allow this device to achieve high performance and low power dissipation. This DRAM operates with a single 3.3 +/-0.3V power supply and interfaces with either LVTTL or LVCMOS levels.

Advanced Information

• 4 194 304 words by 16-bit organization

• 0 to 70 °C operating temperature

• Fast Page Mode operation

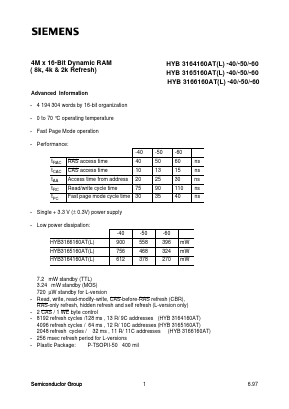

• Performance:

• Single + 3.3 V (± 0.3V) power supply

• Low power dissipation:

7.2 mW standby (TTL)

3.24 mW standby (MOS)

720 µW standby for L-version

• Read, write, read-modify-write, CAS-before-RAS refresh (CBR), RAS-only refresh, hidden refresh and self refresh (L-version only)

• 2 CAS / 1 WE byte control

• 8192 refresh cycles /128 ms , 13 R/ 9C addresses (HYB 3164160AT)

4096 refresh cycles / 64 ms , 12 R/ 10C addresses (HYB 3165160AT)

2048 refresh cycles / 32 ms , 11 R/ 11C addresses (HYB 3166160AT)

• 256 msec refresh period for L-versions

• Plastic Package: P-TSOPII-50 400 mil