Elpida Memory, Inc

EBE10RD4AEFA 数据手册 ( 数据表 ) - Elpida Memory, Inc

Description

The EBE10RD4AEFA is a 128M words × 72 bits, 1 rank DDR2 SDRAM Module, mounting 18 pieces of DDR2 SDRAM sealed in FBGA (µBGA) package.

Read and write operations are performed at the cross points of the CK and the /CK. This high-speed data

transfer is realized by the 4bits prefetch-pipelined architecture.

FEATUREs

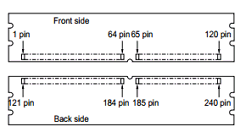

• 240-pin socket type dual in line memory module (DIMM)

PCB height: 30.0mm

Lead pitch: 1.0mm

Lead-free

• Power supply: VDD, VDDQ = 1.8V ± 0.1V

• Data rate: 533Mbps/400Mbps (max.)

• SSTL_18 compatible I/O

• Double-data-rate architecture: two data transfers per clock cycle

• Bi-directional, data strobe (DQS and /DQS) is transmitted /received with data, to be used in capturing data at the receiver

• DQS is edge aligned with data for READs; center aligned with data for WRITEs

• Differential clock inputs (CK and /CK)

• DLL aligns DQ and DQS transitions with CK transitions

• Commands entered on each positive CK edge; data referenced to both edges of DQS

• Four internal banks for concurrent operation (components)

• Burst length: 4, 8

• /CAS latency (CL): 3, 4, 5

• Auto precharge option for each burst access

• Auto refresh and self refresh modes

• Average refresh period

7.8µs at 0°C ≤ TC ≤ +85°C

3.9µs at +85°C < TC ≤ +95°C

• Posted CAS by programmable additive latency for better command and data bus efficiency

• Off-Chip-Driver Impedance Adjustment and On-Die Termination for better signal quality

• /DQS can be disabled for single-ended Data Strobe operation

• 1 piece of PLL clock driver, 2 pieces of register driver and 1 piece of serial EEPROM (2k bits EEPROM) for

Presence Detect (PD)