Dallas Semiconductor -> Maxim Integrated

DS3251 数据手册 ( 数据表 ) - Dallas Semiconductor -> Maxim Integrated

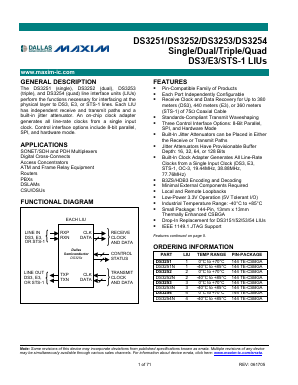

GENERAL DESCRIPTION

The DS3251 (single), DS3252 (dual), DS3253 (triple), and DS3254 (quad) line interface units (LIUs) perform the functions necessary for interfacing at the physical layer to DS3, E3, or STS-1 lines. Each LIU has independent receive and transmit paths and a built-in jitter attenuator. An on-chip clock adapter generates all line-rate clocks from a single input clock. Control interface options include 8-bit parallel, SPI, and hardware mode.

FEATURES

■ Pin-Compatible Family of Products

■ Each Port Independently Configurable

■ Receive Clock and Data Recovery for Up to 380 meters (DS3), 440 meters (E3), or 360 meters (STS-1) of 75Ω Coaxial Cable

■ Standards-Compliant Transmit Waveshaping

■ Three Control Interface Options: 8-Bit Parallel, SPI, and Hardware Mode

■ Built-In Jitter Attenuators can be Placed in Either the Receive or Transmit Paths

■ Jitter Attenuators Have Provisionable Buffer Depth: 16, 32, 64, or 128 Bits

■ Built-In Clock Adapter Generates All Line-Rate Clocks from a Single Input Clock (DS3, E3, STS-1, OC-3, 19.44MHz, 38.88MHz, 77.76MHz)

■ B3ZS/HDB3 Encoding and Decoding

■ Minimal External Components Required

■ Local and Remote Loopbacks

■ Low-Power 3.3V Operation (5V Tolerant I/O)

■ Industrial Temperature Range: -40°C to +85°C

■ Small Package: 144-Pin, 13mm x 13mm Thermally Enhanced CSBGA

■ Drop-In Replacement for DS3151/52/53/54 LIUs

■ IEEE 1149.1 JTAG Support

APPLICATIONS

SONET/SDH and PDH Multiplexers

Digital Cross-Connects

Access Concentrators

ATM and Frame Relay Equipment

Routers

PBXs

DSLAMs

CSU/DSUs