Minicircuits

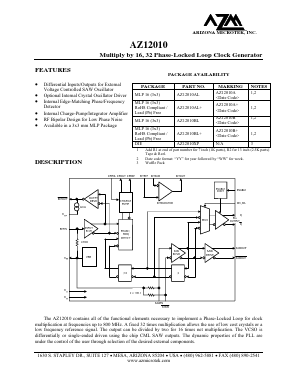

AZ12010AL 数据手册 ( 数据表 ) - Minicircuits

DESCRIPTION

The AZ12010 contains all of the functional elements necessary to implement a Phase-Locked Loop for clock multiplication at frequencies up to 800 MHz. A fixed 32 times multiplication allows the use of low cost crystals or a low frequency reference signal. The output can be divided by two for 16 times net multiplication. The VCSO is differentially or single-ended driven using the chip CML SAW outputs. The dynamic properties of the PLL are under the control of the user through selection of the desired external components.

FEATURES

• Differential Inputs/Outputs for External Voltage Controlled SAW Oscillator

• Optional Internal Crystal Oscillator Driver Internal Edge-Matching Phase/Frequency Detector

• Internal Charge-Pump/Integrator Amplifier

• RF Bipolar Design for Low Phase Noise

• Available in a 3x3 mm MLP Package