Alliance Semiconductor

AS7C513-15TC 数据手册 ( 数据表 ) - Alliance Semiconductor

Functional description

The AS7C513 is a high performance CMOS 524,288-bit Static Random Access Memory (SRAM) organized as 32,768 words × 16 bits. It is designed for memory applications where fast data access, low power, and simple interfacing are desired.

Equal address access and cycle times (tAA, tRC, tWC) of 10/12/15/20 ns with output enable access times (tOE) of 5/6/8/10 ns are ideal for high performance applications. The chip enable input CE permits easy memory expansion with multiple-bank memory systems.

FEATUREs

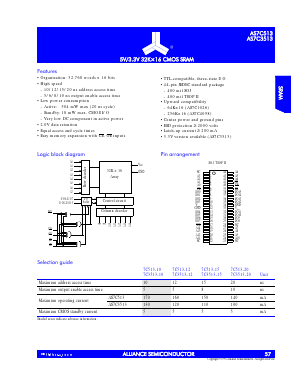

• Organization: 32,768 words × 16 bits

• High speed

- 10/12/15/20 ns address access time

- 5/6/8/10 ns output enable access time

• Low power consumption

- Active: 504 mW max (20 ns cycle)

- Standby: 18 mW max, CMOS I/O

- Very low DC component in active power

• 2.0V data retention

• Equal access and cycle times

• Easy memory expansion with CE, OE inputs

• TTL-compatible, three-state I/O

• 44-pin JEDEC standard package

- 400 mil SOJ

- 400 mil TSOP II

• Upward compatibility

- 64K×16 (AS7C1026)

- 256K×16 (AS7C4098)

• Center power and ground pins

• ESD protection ≥ 2000 volts

• Latch-up current ≥ 200 mA

• 3.3V version available (AS7C3513)