Analog Devices

AD9516-0(RevC) 数据手册 ( 数据表 ) - Analog Devices

GENERAL DESCRIPTION

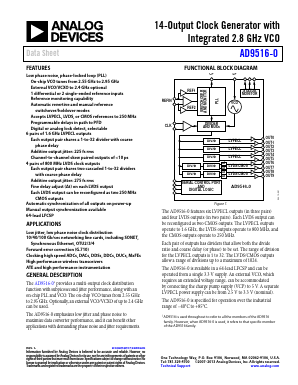

The AD9516-01 provides a multi-output clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 2.55 GHz to 2.95 GHz. Optionally, an external VCO/VCXO of up to 2.4 GHz can be used.

The AD9516-0 emphasizes low jitter and phase noise to maximize data converter performance, and it can benefit other applications with demanding phase noise and jitter requirements.

The AD9516-0 features six LVPECL outputs (in three pairs) and four LVDS outputs (in two pairs). Each LVDS output can be reconfigured as two CMOS outputs. The LVPECL outputs operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and the CMOS outputs operate to 250 MHz.

FEATURES

Low phase noise, phase-locked loop (PLL)

On-chip VCO tunes from 2.55 GHz to 2.95 GHz

External VCO/VCXO to 2.4 GHz optional

1 differential or 2 single-ended reference inputs

Reference monitoring capability

Automatic revertive and manual reference

switchover/holdover modes

Accepts LVPECL, LVDS, or CMOS references to 250 MHz

Programmable delays in path to PFD

Digital or analog lock detect, selectable

6 pairs of 1.6 GHz LVPECL outputs

Each output pair shares a 1-to-32 divider with coarse

phase delay

Additive output jitter: 225 fs rms

Channel-to-channel skew paired outputs of <10 ps

4 pairs of 800 MHz LVDS clock outputs

Each output pair shares two cascaded 1-to-32 dividers

with coarse phase delay

Additive output jitter: 275 fs rms

Fine delay adjust (Δt) on each LVDS output

Each LVDS output can be reconfigured as two 250 MHz

CMOS outputs

Automatic synchronization of all outputs on power-up

Manual output synchronization available

64-lead LFCSP

APPLICATIONS

Low jitter, low phase noise clock distribution

10/40/100 Gb/sec networking line cards, including SONET,

Synchronous Ethernet, OTU2/3/4

Forward error correction (G.710)

Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs

High performance wireless transceivers

ATE and high performance instrumentation