Integrated Device Technology

83940DKILF(2013) 数据手册 ( 数据表 ) - Integrated Device Technology

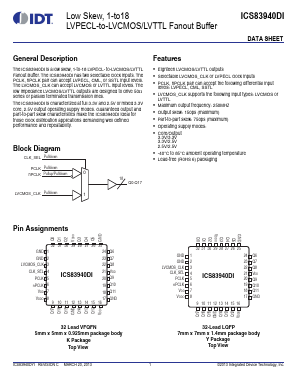

General Description

The ICS83940DI is a low skew, 1-to-18 LVPECL- to-LVCMOS/LVTTL Fanout Buffer. The ICS83940DI has two selectable clock inputs. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The LVCMOS_CLK can accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/LVTTL outputs are designed to drive 50 series or parallel terminated transmission lines.

FEATUREs

• Eighteen LVCMOS/LVTTL outputs

• Selectable LVCMOS_CLK or LVPECL clock inputs

• PCLK, nPCLK pair can accept the following differential input levels: LVPECL, CML, SSTL

• LVCMOS_CLK supports the following input types: LVCMOS or LVTTL

• Maximum output frequency: 250MHz

• Output skew: 150ps (maximum)

• Part-to-part skew: 750ps (maximum)

• Operating supply modes:

• Core/Output

3.3V/3.3V

3.3V/2.5V

2.5V/2.5V

• -40°C to 85°C ambient operating temperature

• Lead-free (RoHS 6) packaging