Hitachi -> Renesas Electronics

74LV175 数据手册 ( 数据表 ) - Hitachi -> Renesas Electronics

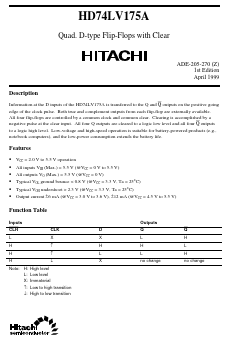

Description

Information at the D inputs of the HD74LV175A is transferred to the Q and Q outputs on the positive going edge of the clock pulse. Both true and complement outputs from each flip-flop are externally available. All four flip-flops are controlled by a common clock and common clear. Clearing is accomplished by a negative pulse at the clear input. All four Q outputs are cleared to a logic low level and all four Q outputs to a logic high level. Low-voltage and high-speed operation is suitable for battery-powered products (e.g., notebook computers), and the low-power consumption extends the battery life.

FEATUREs

• VCC = 2.0 V to 5.5 V operation

• All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V)

• All outputs VO (Max.) = 5.5 V (@VCC = 0 V)

• Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

• Typical VOH undershoot > 2.3 V (@VCC = 3.3 V, Ta = 25°C)

• Output current ±6 mA (@VCC = 3.0 V to 3.6 V), ±12 mA (@VCC = 4.5 V to 5.5 V)