Intel

28F128 数据手册 ( 数据表 ) - Intel

Product Overview

The 0.25 µ 3 Volt Intel StrataFlash memory family contains high-density memories organized as 16 Mbytes or 8 Mwords (128-Mbit), 8 Mbytes or 4 Mwords (64-Mbit), and 4 Mbytes or 2 Mwords (32-Mbit). These devices can be accessed as 8- or 16-bit words. The 128-Mbit device is organized as one-hundred-twenty-eight 128-Kbyte (131,072 bytes) erase blocks. The 64-Mbit device is organized as sixty-four 128-Kbyte erase blocks while the 32-Mbits device contains thirty-two 128-Kbyte erase blocks. Blocks are selectively and individually lockable and unlockable in system. A 128-bit protection register has multiple uses, including unique flash device identification.

Product Features

■ High-Density Symmetrically-Blocked Architecture

—128 128-Kbyte Erase Blocks (128 M)

—64 128-Kbyte Erase Blocks (64 M)

—32 128-Kbyte Erase Blocks (32 M)

■ High Performance Interface Asynchronous Page Mode Reads

—110/25 ns Read Access Time (32 M)

—120/25 ns Read Access Time (64 M)

—150/25 ns Read Access Time (128 M)

■ 2.7 V–3.6 V VCC Operation

■ 128-bit Protection Register

—64-bit Unique Device Identifier

—64-bit User Programmable OTP Cells

■ Enhanced Data Protection Features

Absolute Protection with VPEN = GND

—Flexible Block Locking

—Block Erase/Program Lockout during Power Transitions

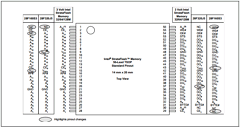

■ Packaging

—56-Lead TSOP Package

—64-Ball Intel® Easy BGA Package

■ Cross-Compatible Command Support Intel Basic Command Set

—Common Flash Interface

—Scalable Command Set

■ 32-Byte Write Buffer

—6 µs per Byte Effective Programming Time

■ 12.8M Total Min. Erase Cycles (128 Mbit)

6.4M Total Min. Erase Cycles (64 Mbit)

3.2M Total Min. Erase Cycles (32 Mbit)

—100K Minimum Erase Cycles per Block

■ Automation Suspend Options

—Block Erase Suspend to Read

—Block Erase Suspend to Program

—Program Suspend to Read

■ 0.25 µ Intel® StrataFlash™ Memory Technology