MM74C240 查看數據表(PDF) - Fairchild Semiconductor

零件编号

产品描述 (功能)

生产厂家

MM74C240

Fairchild Semiconductor

MM74C240 Datasheet PDF : 8 Pages

| |||

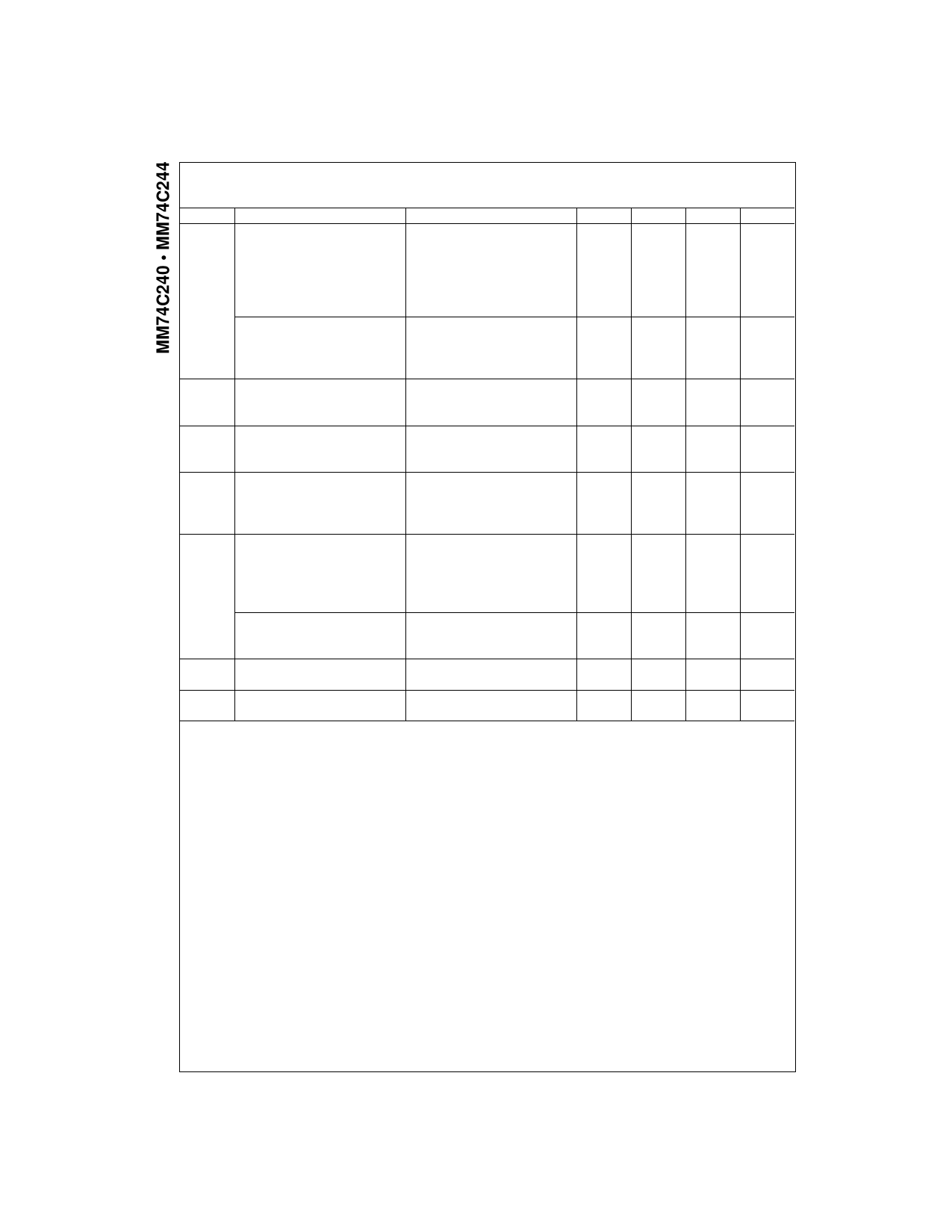

AC Electrical Characteristics (Note 2)

TA = 25°C, CL = 50 pF, unless otherwise specified

Symbol

Parameter

Conditions

Min

Typ

Max

Units

tPD(1),

tPD(0)

Propagation Delay

(Data In to Out)

MM74C240

MM74C244

t1H, t0H

Propagation Delay Output

Disable to High Impedance

State (from a Logic Level)

tH1, tH0

Propagation Delay Output

Disable to Logic Level

(from High Impedance State)

tT(HL), tT(LH) Transition Time

CPD

Power Dissipation

Capacitance

VCC = 5V, CL = 50 pF

VCC = 10V, CL = 50 pF

V CC = 5V, CL = 150 pF

VCC = 10V, CL = 150 pF

V CC = 5V, CL = 50 pF

VCC = 10V, CL = 50 pF

VCC = 5V, CL = 150 pF

VCC = 10V, CL = 150 pF

RL = 1k, CL = 50 pF

VCC = 5V

VCC = 10V

RL = 1k, CL = 50 pF

VCC = 5V

VCC = 10V

VCC = 5V, CL = 50 pF

VCC = 10V, CL = 50 pF

VCC = 5V, CL = 150 pF

VCC = 10V, CL = 150 pF

(Note 3)

60

90

40

70

ns

80

110

60

90

45

70

25

50

ns

60

90

40

70

45

80

ns

35

60

50

90

ns

30

60

45

80

30

60

ns

75

140

50

100

(Output Enabled per Buffer)

MM74C240

MM74C244

100

pF

100

(Output Disabled per Buffer)

MM74C240

MM74C244

10

pF

0

CIN

Input Capacitance (Note 4)

(Any Input)

VIN = 0V, f = 1 MHz, TA = 25°C

10

pF

CO

Output Capacitance (Note 4)

(Output Disabled)

VIN = 0V, f = 1 MHz, TA = 25°C

10

pF

Note 2: AC Parameters are guaranteed by DC correlated testing.

Note 3: CPD determines the no load AC power consumption of any CMOS device. For complete explanation see Family Characteristics Application Note,

AN-90.

Note 4: Capacitance is guaranteed by periodic testing.

www.fairchildsemi.com

4