8701CYILF 查看數據表(PDF) - Integrated Device Technology

零件编号

产品描述 (功能)

生产厂家

8701CYILF Datasheet PDF : 14 Pages

| |||

ICS8701I

LOW SKEW, ÷1, ÷2

CLOCK GENERATOR

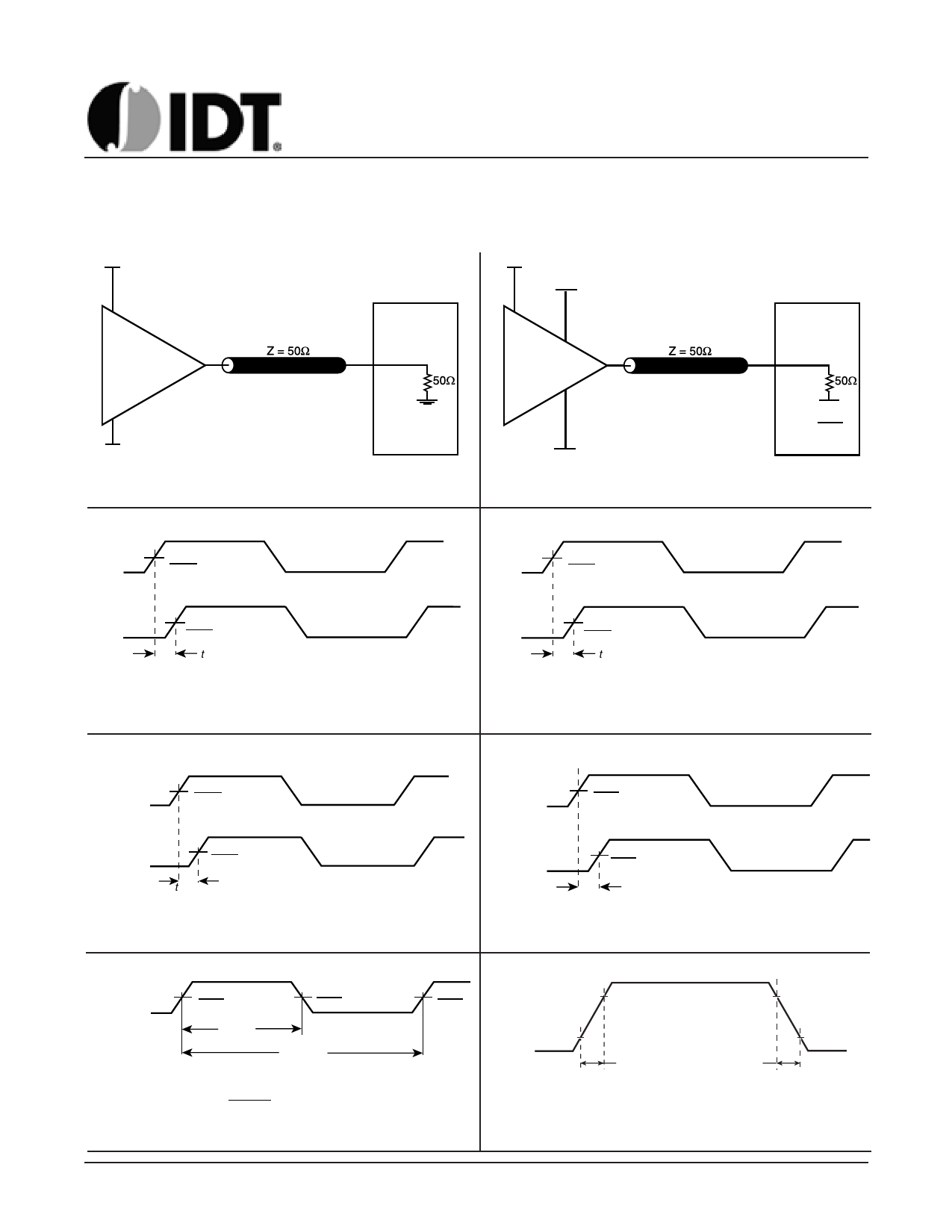

PARAMETER MEASUREMENT INFORMATION

1.65V±5%

VDD,

VDDO

LVCMOS

GND

SCOPE

Qx

-1.165V±5%

3.3V CORE/3.3V OUTPUT LOAD AC TEST CIRCUIT

V

DDO

Qx

2

V

DDO

Qy

2

t sk(o)

2.05V±5%

1.25V±5%

VDD

V

DDO

LVCMOS

GND

-1.25V±5%

SCOPE

Qx

VDDO

2

3.3V CORE/2.5V OUTPUT LOAD AC TEST CIRCUIT

Part 1

Qx

Part 2

Qy

V

DDO

2

V

DDO

2

t sk(pp)

OUTPUT SKEW

PART-TO-PART SKEW

QX0:QX4

VDDO

2

VDD

CLK

2

QX0:QX4

VDDO

2

t sk(b)

QA0:QA4,

QB0:QB4,

QC0:QC4,

QD0:QD4

VDDO

2

t

PD

BANK SKEW (where X denotes outputs in the same bank)

PROPAGATION DELAY

QA0:QA4,

QB0:QB4,

QC0:QC4,

QD0:QD4

VDDO

2

t PW

VDDO

2

t PERIOD

odc = t PW

t PERIOD

OUTPUT DUTY CYCLE/PULSE WIDTH/PERIIOD

8701CYI

VDDO

2

30%

Clock

Outputs

70%

tR

OUTPUT RISE/FALL TIME

www.idt.com

8

70%

tF

30%

REV. C JULY 27, 2010