740L6010(2003) 查看數據表(PDF) - Fairchild Semiconductor

零件编号

产品描述 (功能)

生产厂家

740L6010 Datasheet PDF : 15 Pages

| |||

HIGH-SPEED

LOGIC-TO-LOGIC OPTOCOUPLERS

LSTTL TO

TTL BUFFER

TTL INVERTER

CMOS BUFFER

CMOS INVERTER

74OL6000

74OL6001

74OL6010

74OL6011

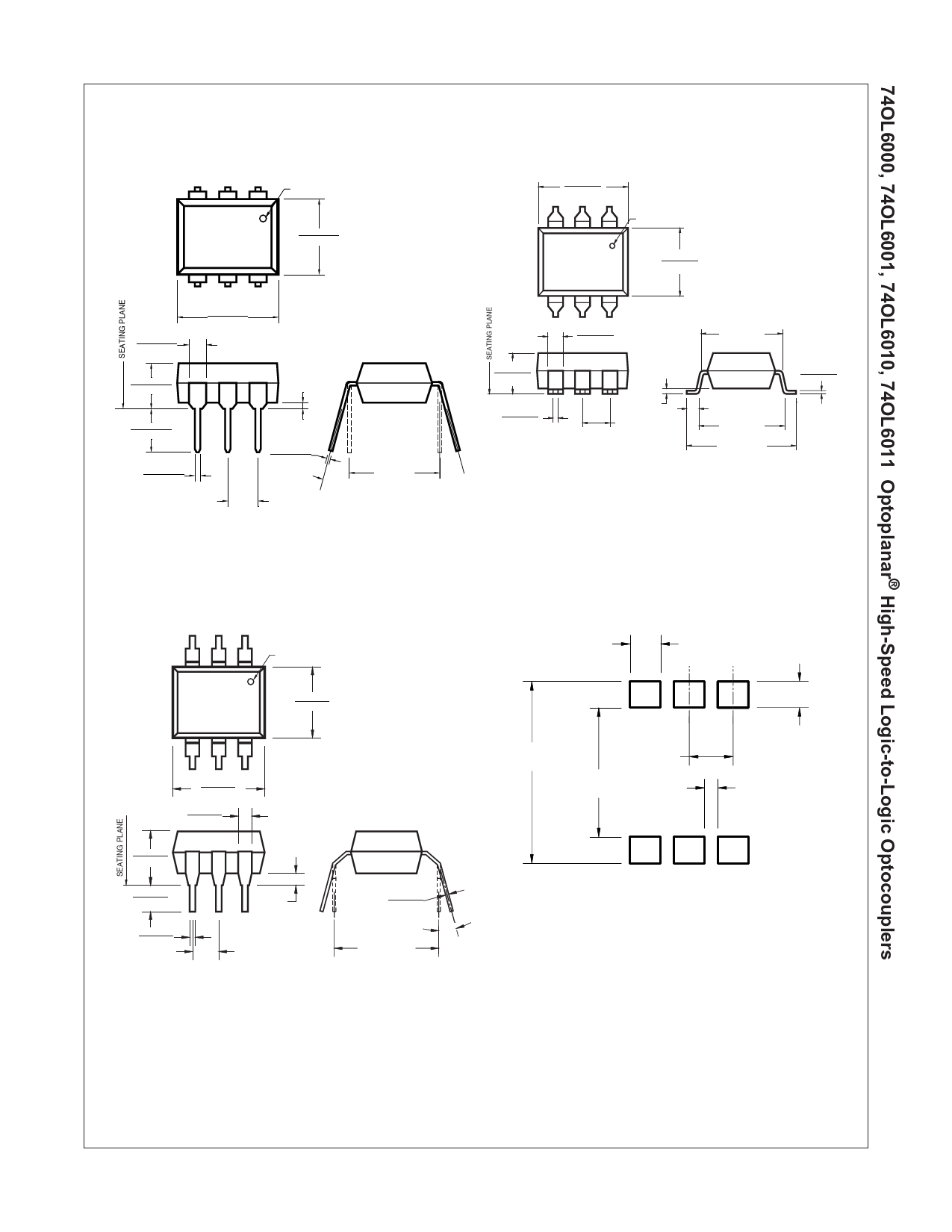

Package Dimensions (Through Hole)

PIN 1

ID.

0.270 (6.86)

0.240 (6.10)

0.070 (1.78)

0.045 (1.14)

0.350 (8.89)

0.330 (8.38)

0.200 (5.08)

0.115 (2.92)

0.154 (3.90)

0.100 (2.54)

0.022 (0.56)

0.016 (0.41)

0.100 (2.54)

TYP

0.020 (0.51)

MIN

0.016 (0.40)

0.008 (0.20)

0° to 15°

0.300 (7.62)

TYP

Package Dimensions (0.4” Lead Spacing)

PIN 1

ID.

0.270 (6.86)

0.240 (6.10)

0.350 (8.89)

0.330 (8.38)

0.070 (1.78)

0.045 (1.14)

0.200 (5.08)

0.135 (3.43)

0.154 (3.90)

0.100 (2.54)

0.022 (0.56)

0.016 (0.41)

0.004 (0.10)

MIN

0.100 (2.54) TYP

0.016 (0.40)

0.008 (0.20)

0° to 15°

0.400 (10.16)

TYP

NOTE

All dimensions are in inches (millimeters)

Package Dimensions (Surface Mount)

0.350 (8.89)

0.330 (8.38)

3

2

1

PIN 1

ID.

0.270 (6.86)

0.240 (6.10)

4

5

6

0.070 (1.78)

0.045 (1.14)

0.200 (5.08)

0.165 (4.18)

0.022 (0.56)

0.016 (0.41)

0.020 (0.51)

MIN

0.100 (2.54)

TYP

Lead Coplanarity : 0.004 (0.10) MAX

0.300 (7.62)

TYP

0.016 (0.40) MIN

0.315 (8.00)

MIN

0.405 (10.30)

MAX

0.016 (0.41)

0.008 (0.20)

Recommended Pad Layout for

Surface Mount Leadform

0.070 (1.78)

0.060 (1.52)

0.415 (10.54)

0.100 (2.54)

0.295 (7.49)

0.030 (0.76)

© 2003 Fairchild Semiconductor Corporation

Page 11 of 15

3/19/03