CS62180B-IL 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

生产厂家

CS62180B-IL Datasheet PDF : 50 Pages

| |||

CS62180B

7 (MSB) 6

OOFD3 OOFD2

OOF Count

5

4

OOFD1 OOFD0

Presetable.

Saturates at 15 (1111).

3

2

ESFD3 ESFD2

ESF Error Count

1

0 (LSB)

ESFD1 EFSD0

Presetable.

Saturates at 15 (1111).

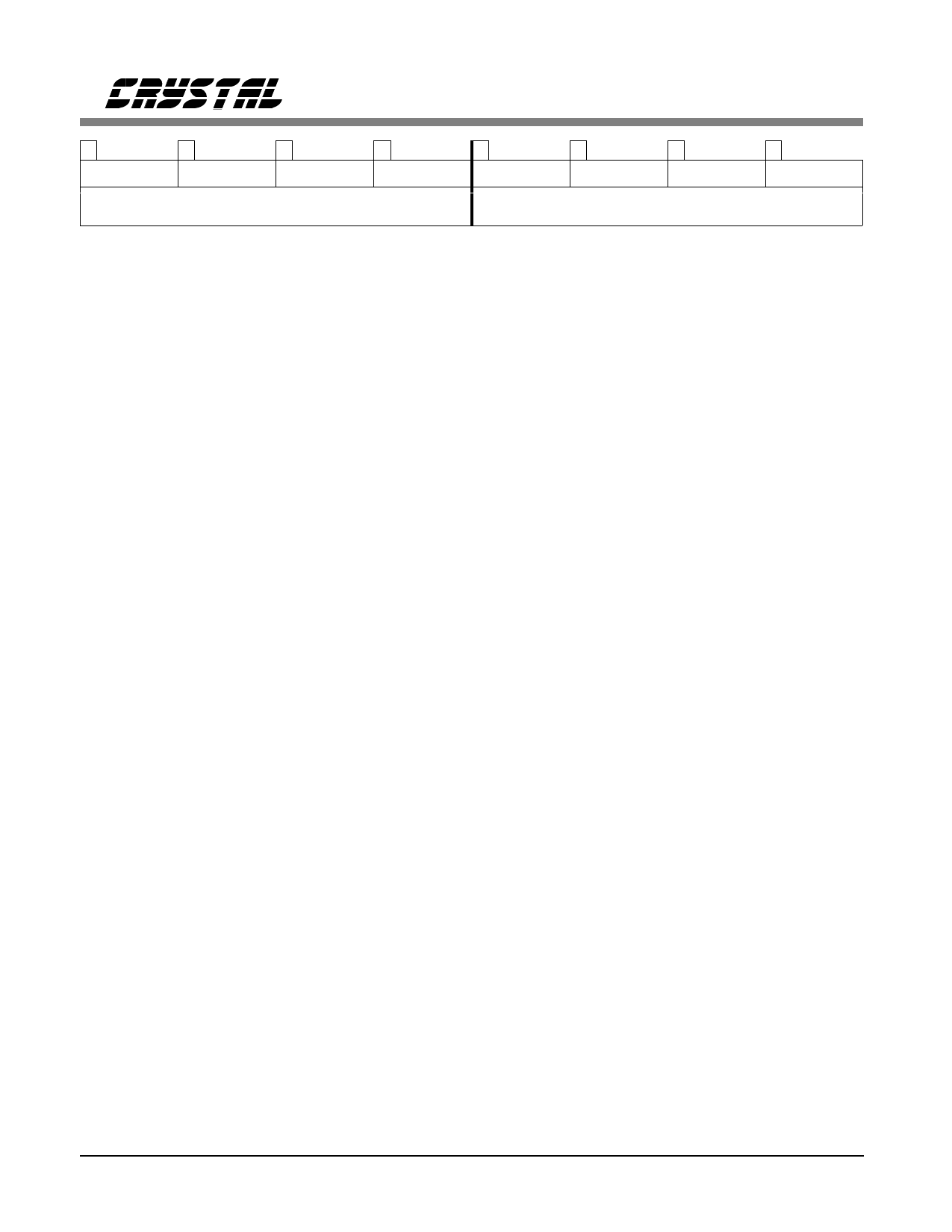

Figure 23. Error Count Register (ECR)

When using a bit 2 yellow alarm, in either 193S

or 193E mode, a yellow alarm is defined as a

"0" in bit 2 (2nd MSB) of every DS0 channel.

RYEL will signal a bit 2 yellow alarm when 256

or more consecutive channels are detected with a

"0" in bit 2. The alarm will clear at the next "1"

detected in a bit 2 position.

When using an FDL yellow alarm in 193E

mode, RYEL will declare a yellow alarm after

16 repetitions of "00FF" on the FDL. The alarm

will clear at the next bit which is out of se-

quence.

When using an S-bit yellow alarm in 193S

mode, RYEL will transition high whenever a "1"

is detected in the F-bit of frame 12. The alarm is

not cleared until a zero is detected in the F-bit of

frame 12.

In T1DM mode , a yellow alarm is detected by

checking the channel 24 sync word. In SLC-96®

mode, the CS62180B does not recognize yellow

alarms, rather, they are recognized by the user

via the DL.

Error Count Saturation

RSR.6: ECS

ECS (RSR.6) monitors the status of the Error

Count Register (ECR), as shown in Figure 23.

The ECR provides two, separate, 4 bit counters

at one register address: the ESF Error Count (D0

- D3), and the OOF Count (D4 - D7). RSR.6

will go high after either of these 4 bit counters

becomes saturated (at 15), and new OOF or ESF

event is detected (the 16th or greater).

The OOF Counter (D4 - D7) records the number

of out-of-frame events. An OOF event occurs

when 2 out of either 4 or 5 consecutive framing

bits are in error, as defined by RCR.6. In 193S

mode, the FT bits are monitored for OOF events,

while in 193E mode, the FPS bits are used.

The ESF counter (D0 - D3) records the number

of "Errored Superframes". An ESF event in 193E

mode is defined as an OOF event, or a CRC er-

ror. The ESF counter will be advanced each time

either event is detected. In 193S mode, the ESF

counter records individual framing bit errors. If

RCR.3 is set, requiring FS bits to be qualified for

synchronization, both FT and FS bit errors will

advance the ESF counter. If RCR.3 is clear, only

FT bits will be monitored.

The OOF and ESF operate separately, each

counting up from 0 (hex) and saturating at F

(hex). The saturation threshold can be changed

for each counter separately, by presetting the

counter to some value higher than 0. Because

they share the same register address, both count-

ers must be read or written simultaneously.

There is no status pin directly corresponding to

the ECS bit, but FERR signals individual frame

bit and CRC errors, and RLOS signals an OOF

event. ECS counter increments are disabled

when resync is in progress (RLOS high).

Bipolar Violation Count Saturation

RSR.7: BVCS

Individual Bipolar Violations are recorded in an

8 bit counter, the Bipolar Violation Count Regis-

ter (BVCR), as show in Figure 24. The BVCR

counts up from 0 (all "0’s") to 255 (all "1’s").

After reaching saturation at 255, every Bipolar

DS225PP2

31