PEB2084 查看數據表(PDF) - Siemens AG

零件编号

产品描述 (功能)

生产厂家

PEB2084 Datasheet PDF : 72 Pages

| |||

PEB 2084

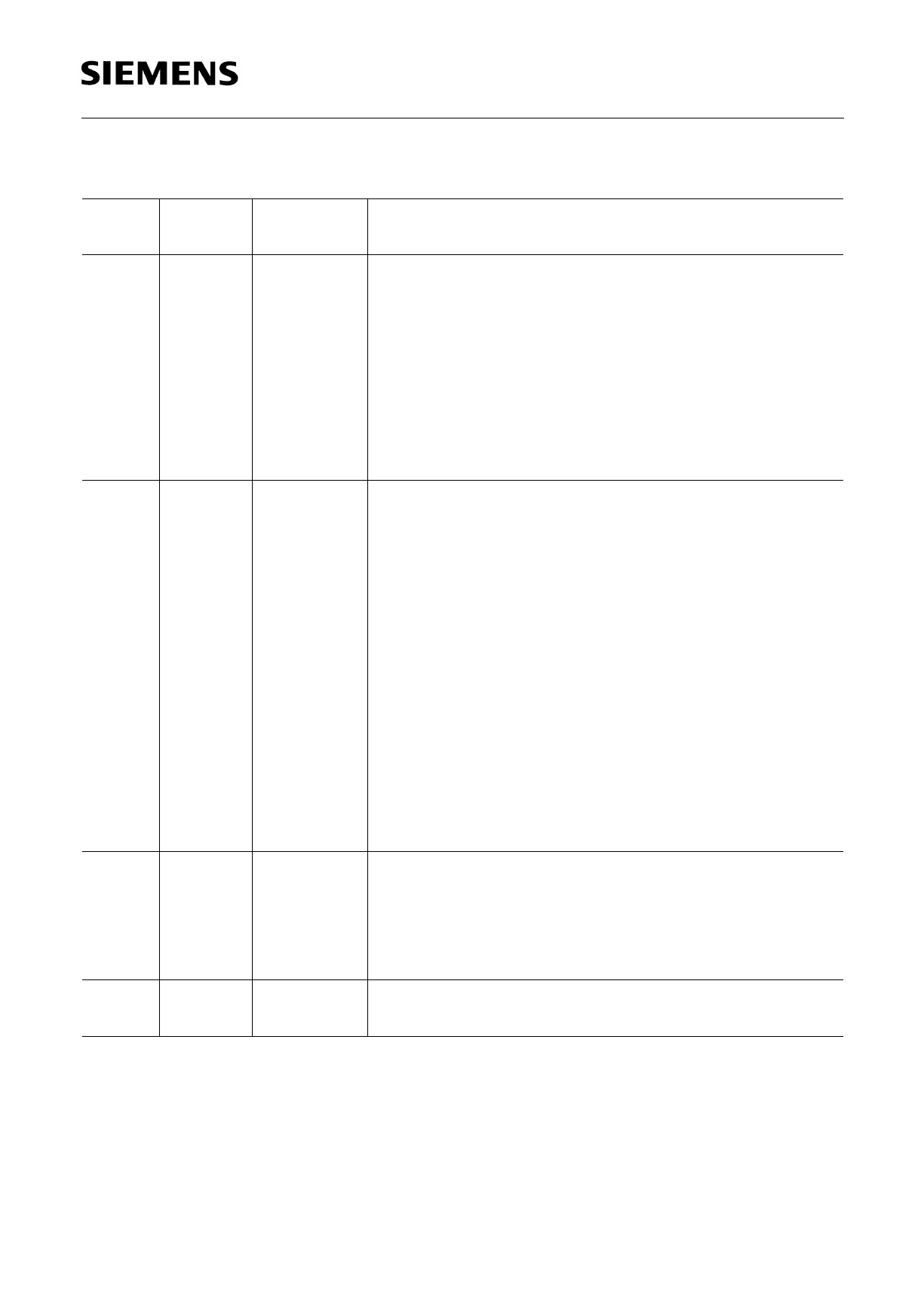

1.4 Pin Description

Pin No. Symbol Input (I) Function

Output (O)

29, 30 SR0a,b I

32, 33 SX0a,b O

27, 26 SR1a,b I

24, 23 SX1a,b O

5, 4 SR2a,b I

2, 1 SX2a,b O

7, 8 SR3a,b I

10, 11 SX3a,b O

S/T Interface a: positive, b: negative

No. 0: differential input

No. 0: differential output

No. 1: differential input

No. 1: differential output

No. 2: differential input

No. 2: differential output

No. 3: differential input

No. 3: differential output

43

FSC

I

42

DCL

I

41

IDI

I

40

IDO

O/I

39

ICS

I

IOM®-2 Interface

Frame Synchronization Clock (8 kHz)

Data Clock

IOM Interface Data Input: Data Downstream in LT-S

Data Upstream in LT-T

IOM Interface Data Output: Data Upstream in LT-S

Data Downstream in LT-T

Output

open-drain: resistor to VDD

push-pull: resistor to VSS

resistor = 100 kΩ to 1 MΩ

refer to push-pull sensing, chapter 3.2

IOM Interface Channel Select (pin-strapping)

0: channels 0 though 3 selected

1: channels 4 through 7 selected

16

TMS I

15

TCK

I

14

TDI

I

13

TDO

O

JTAG Boundary Scan Test Interface

Test Mode Select

Test Clock 6.25 MHz

Test Data Input

Test Data Output

20

XTAL1 I

21

XTAL2 O

Oscillator or 7.68 MHz clock input

Oscillator output

Semiconductor Group

11