CY7C68053 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

生产厂家

CY7C68053 Datasheet PDF : 42 Pages

| |||

CY7C68053

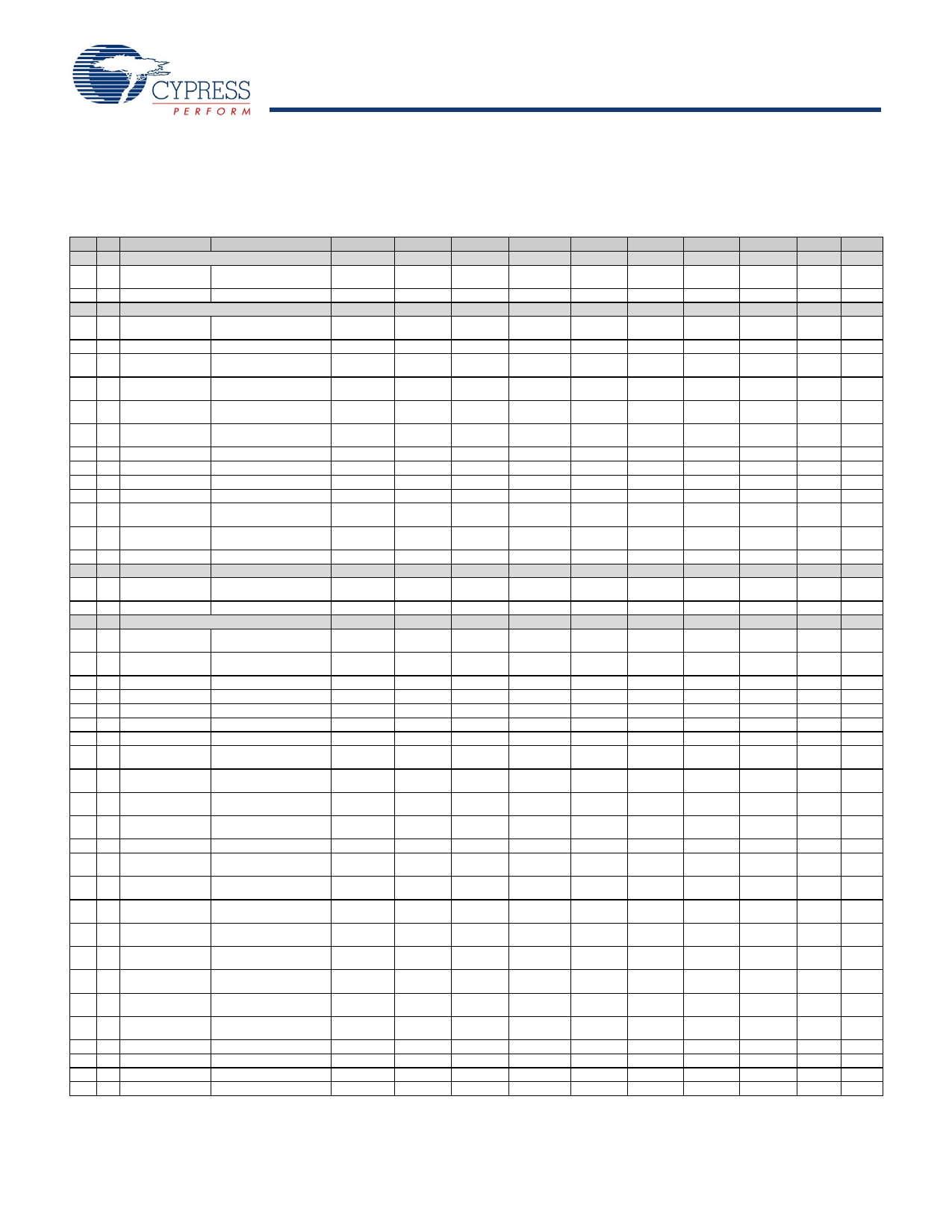

5. Register Summary

FX2LP18 register bit definitions are described in the MoBL-USB FX2LP18 TRM in greater detail.

Table 8. FX2LP18 Register Summary

Hex Size Name

Description

GPIF Waveform Memories

E400 128 WAVEDATA

GPIF Waveform

descriptor 0, 1, 2, 3 data

E480 128 Reserved

GENERAL CONFIGURATION

E50D

GPCR2

General Purpose Configura-

tion Register 2

E600 1 CPUCS

CPU Control and Status

E601 1 IFCONFIG

E602 1 PINFLAGSAB[10]

E603 1 PINFLAGSCD[10]

E604 1 FIFORESET[10]

Interface Configuration

(Ports, GPIF, Slave FIFOs)

Slave FIFO FLAGA and

FLAGB pin configuration

Slave FIFO FLAGC and

FLAGD pin configuration

Restore FIFOs to default

state

E605 1 BREAKPT

Breakpoint control

E606 1 BPADDRH

Breakpoint address H

E607 1 BPADDRL

Breakpoint address L

E608

E609

1 Reserved

Reserved

1 FIFOPINPOLAR[10] Slave FIFO interface pins

polarity

E60A 1 REVID

Chip revision

b7

D7

Reserved

0

IFCLKSRC

FLAGB3

FLAGD3

NAKALL

0

A15

A7

0

0

rv7

E60B

E60C

E610

E611

E612

E613

E614

E615

E618

E619

E61A

E61B

E61C

E620

E621

E622

E623

E624

E625

E626

E627

E628

E629

E62A

E62B

1 REVCTL[10]

Chip revision control

UDMA

1 GPIFHOLDAMOUNT MSTB hold time

(for UDMA)

3 Reserved

ENDPOINT CONFIGURATION

1 EP1OUTCFG

Endpoint 1-OUT

configuration

1 EP1INCFG

Endpoint 1-IN

configuration

1 EP2CFG

Endpoint 2 configuration

1 EP4CFG

Endpoint 4 configuration

1 EP6CFG

Endpoint 6 configuration

1 EP8CFG

Endpoint 8 configuration

2 Reserved

1 EP2FIFOCFG[10]

1 EP4FIFOCFG[10]

1 EP6FIFOCFG[10]

1 EP8FIFOCFG[10]

Endpoint 2/Slave FIFO

configuration

Endpoint 4/Slave FIFO

configuration

Endpoint 6/Slave FIFO

configuration

Endpoint 8/Slave FIFO

configuration

4 Reserved

1 EP2AUTOINLENH[10 Endpoint 2 AUTOIN

packet length H

1 EP2AUTOINLENL[10] Endpoint 2 AUTOIN

packet length L

1 EP4AUTOINLENH[10 Endpoint 4 AUTOIN

]

packet length H

1 EP4AUTOINLENL[10] Endpoint 4 AUTOIN

packet length L

1 EP6AUTOINLENH[10 Endpoint 6 AUTOIN

]

packet length H

1 EP6AUTOINLENL[10] Endpoint 6 AUTOIN

packet length L

1 EP8AUTOINLENH[10 Endpoint 8 AUTOIN

]

packet length H

1 EP8AUTOINLENL[10] Endpoint 8 AUTOIN

packet length L

1 ECCCFG

ECC Configuration

1 ECCRESET

ECC Reset

1 ECC1B0

ECC1 Byte 0 address

1 ECC1B1

ECC1 Byte 1 address

0

0

VALID

VALID

VALID

VALID

VALID

VALID

0

0

0

0

0

PL7

0

PL7

0

PL7

0

PL7

0

x

LINE15

LINE7

b6

b5

b4

b3

b2

b1

b0 Default Access

D6

D5

D4

D3

D2

D1

D0 xxxxxxxx RW

Reserved

0

3048MHZ

Reserved FULL_SPEED Reserved

_ONLY

PORTCSTB CLKSPD1 CLKSPD0

IFCLKOE IFCLKPOL ASYNC

Reserved

CLKINV

GSTATE

Reserved

CLKOE

IFCFG1

Reserved 00000000 R

8051RES 00000010 rrbbbbbr

IFCFG0 10000000 RW

FLAGB2 FLAGB1 FLAGB0 FLAGA3 FLAGA2 FLAGA1 FLAGA0 00000000 RW

FLAGD2 FLAGD1 FLAGD0 FLAGC3 FLAGC2 FLAGC1 FLAGC0 00000000 RW

0

0

0

EP3

EP2

EP1

EP0 xxxxxxxx W

0

0

0

BREAK BPPULSE BPEN

A14

A13

A12

A11

A10

A9

A6

A5

A4

A3

A2

A1

0

0

0

0

0

0

0

PKTEND

SLOE

SLRD

SLWR

EF

0

00000000 rrrrbbbr

A8 xxxxxxxx RW

A0 xxxxxxxx RW

0

00000000 rrrrrrbb

FF 00000000 rrbbbbbb

rv6

rv5

rv4

rv3

rv2

rv1

rv0 RevA R

00000001

0

0

0

0

0

dyn_out enh_pkt 00000000 rrrrrrbb

0

0

0

0

0

HOLDTIME1 HOLDTIME0 00000000 rrrrrrbb

0

0

DIR

DIR

DIR

DIR

INFM1

INFM1

INFM1

INFM1

TYPE1

TYPE0

0

0

0

0

10100000 brbbrrrr

TYPE1

TYPE0

0

0

0

0

10100000 brbbrrrr

TYPE1

TYPE0

SIZE

0

BUF1

BUF0 10100010 bbbbbrbb

TYPE1

TYPE0

0

0

0

0

10100000 bbbbrrrr

TYPE1

TYPE0

SIZE

0

BUF1

BUF0 11100010 bbbbbrbb

TYPE1

TYPE0

0

0

0

0

11100000 bbbbrrrr

OEP1

AUTOOUT AUTOIN ZEROLENIN

0

WORDWIDE 00000101 rbbbbbrb

OEP1

AUTOOUT AUTOIN ZEROLENIN

0

WORDWIDE 00000101 rbbbbbrb

OEP1

AUTOOUT AUTOIN ZEROLENIN

0

WORDWIDE 00000101 rbbbbbrb

OEP1

AUTOOUT AUTOIN ZEROLENIN

0

WORDWIDE 00000101 rbbbbbrb

0

PL6

0

PL6

0

PL6

0

PL6

0

x

LINE14

LINE6

0

PL5

0

PL5

0

PL5

0

PL5

0

x

LINE13

LINE5

0

PL4

0

PL4

0

PL4

0

PL4

0

x

LINE12

LINE4

0

PL3

0

PL3

0

PL3

0

PL3

0

x

LINE11

LINE3

PL10

PL2

0

PL2

PL10

PL2

0

PL2

0

x

LINE10

LINE2

PL9

PL1

PL9

PL1

PL9

PL1

PL9

PL1

0

x

LINE9

LINE1

PL8 00000010 rrrrrbbb

PL0 00000000 RW

PL8 00000010 rrrrrrbb

PL0 00000000 RW

PL8 00000010 rrrrrbbb

PL0 00000000 RW

PL8 00000010 rrrrrrbb

PL0 00000000 RW

ECCM

x

LINE8

LINE0

00000000 rrrrrrrb

00000000 W

00000000 R

00000000 R

Note

10. Read and writes to these registers may require synchronization delay, see MoBL-USB FX2LP18 Technical Reference Manual for ‘Synchronization Delay.’

Document # 001-06120 Rev *J

Page 17 of 42

[+] Feedback