M74HC113B1R 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

生产厂家

M74HC113B1R Datasheet PDF : 11 Pages

| |||

M74HC113

DUAL J-K FLIP FLOP WITH PRESET

s HIGH SPEED :

fMAX = 79MHz (TYP.) at VCC = 6V

s LOW POWER DISSIPATION:

ICC =2µA(MAX.) at TA=25°C

s HIGH NOISE IMMUNITY:

VNIH = VNIL = 28 % VCC (MIN.)

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s WIDE OPERATING VOLTAGE RANGE:

VCC (OPR) = 2V to 6V

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 113

DESCRIPTION

The M74HC113 is an high speed CMOS DUAL

J-K FLIP FLOP WITH PRESET fabricated with

silicon gate C2MOS technology.

This circuit offers individual J, K, set, and clock

inputs. These monolithic dual flip-flops are

designed so that when the clock goes HIGH, the

inputs are enabled and data will be accepted. The

logic level of the J and K inputs may be allowed to

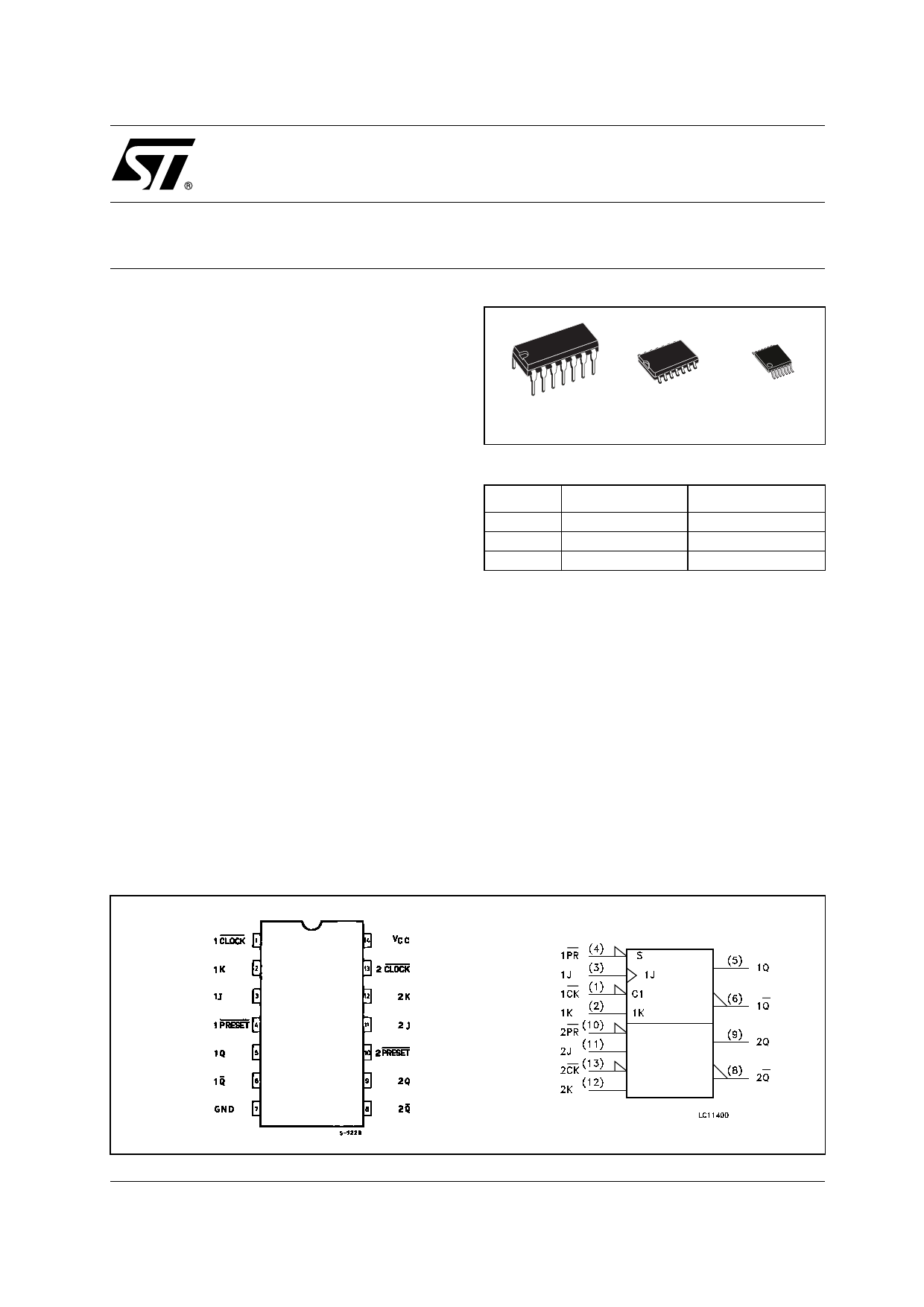

DIP

SOP

TSSOP

ORDER CODES

PACKAGE

TUBE

DIP

SOP

TSSOP

M74HC113B1R

M74HC113M1R

T&R

M74HC113RM13TR

M74HC113TTR

change when the clock pulse is HIGH and the

bistable will function as shown in the truth table as

long as minimum set-up times are observed. Input

data is transferred to the outputs on the negative

going edge of the clock pulse.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

July 2001

1/11