HYB18T256802BF-3.7 查看數據表(PDF) - Infineon Technologies

零件编号

产品描述 (功能)

生产厂家

HYB18T256802BF-3.7 Datasheet PDF : 33 Pages

| |||

Product Type

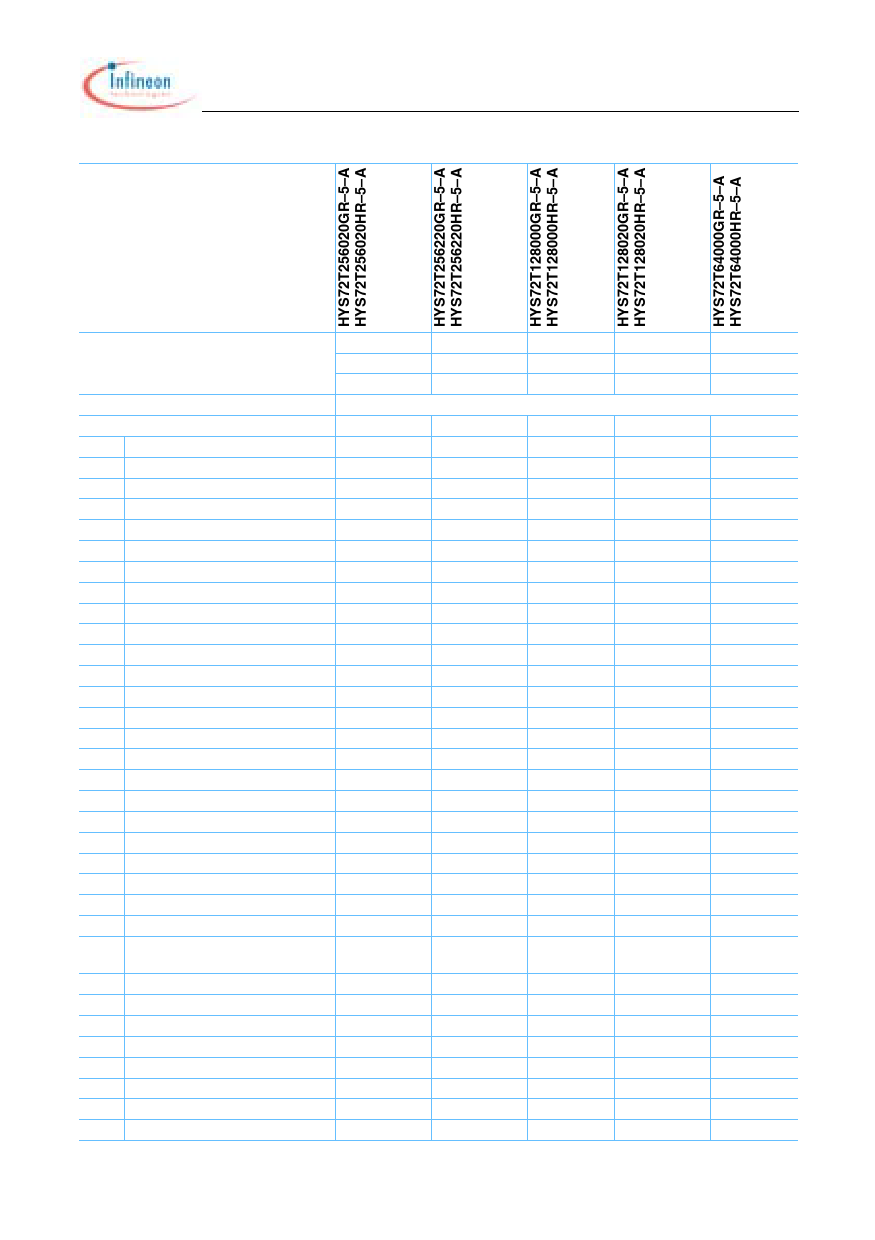

HYS72T[256/128/64][0/2][0/2]0[G/H]R-[5/3.7]-A

Registered DDR2 SDRAM Modules

Organization

Label Code

Jedec SPD Revision

Byte# Description

27

tRP.min [ns]

28

tRRD.min [ns]

29

tRCD.min [ns]

30

tRAS.min [ns]

31 Module Density per Rank

32

tAS.min and tCS.min [ns]

33

tAH.min and tCH.min [ns]

34

tDS.min [ns]

35

tDH.min [ns]

36

tWR.min [ns]

37

tWTR.min [ns]

38

tRTP.min [ns]

39 Analysis Characteristics

40

tRC and tRFC Extension

41

tRC.min [ns]

42

tRFC.min [ns]

43

tCK.max [ns]

44

tDQSQ.max [ns]

45

tQHS.max [ns]

46 PLL Relock Time

47

TCASE.max Delta / ∆T4R4W Delta

48 Psi(T-A) DRAM

49

∆ T0

50

∆ T2N (UDIMM) or ∆ T2Q

(RDIMM)

51

∆ T2P

52

∆ T3N

53

∆ T3P.fast

54

∆ T3P.slow

55

∆ T4R / ∆ T4R4W Sign

56

∆ T5B

57

∆ T7

58 Psi(ca) PLL

2 GByte

2 GByte

1 GByte 1 GByte

512 MB

×72

×72

×72

×72

×72

2 Ranks (×4) 2 Ranks (×4) 1 Rank (×4) 2 Ranks (×8) 1 Rank (×8)

PC2–3200R–333

Rev. 1.1

Rev. 1.1

Rev. 1.1 Rev. 1.1

Rev. 1.1

HEX

HEX

HEX

HEX

HEX

3C

3C

3C

3C

3C

1E

1E

1E

1E

1E

3C

3C

3C

3C

3C

2D

2D

2D

2D

2D

01

01

01

80

80

35

35

35

35

35

47

47

47

47

47

15

15

15

15

15

27

27

27

27

27

3C

3C

3C

3C

3C

28

28

28

28

28

1E

1E

1E

1E

1E

00

00

00

00

00

00

00

00

00

00

3C

3C

3C

3C

3C

69

69

69

69

69

80

80

80

80

80

23

23

23

23

23

2D

2D

2D

2D

2D

0F

0F

0F

0F

0F

51

51

51

51

51

78

78

78

78

78

32

32

32

32

32

1D

1D

1D

1D

1D

1E

1E

1E

1E

1E

1B

1B

1B

1B

1B

1E

1E

1E

1E

1E

17

17

17

17

17

28

28

28

28

28

1B

1B

1B

1B

1B

1E

1E

1E

1E

1E

C4

C4

C4

C4

C4

Data Sheet

Preliminary

24

Rev. 0.85, 2004-04