HCC40102B 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

生产厂家

HCC40102B Datasheet PDF : 13 Pages

| |||

HCC/HCF40102B/40103B

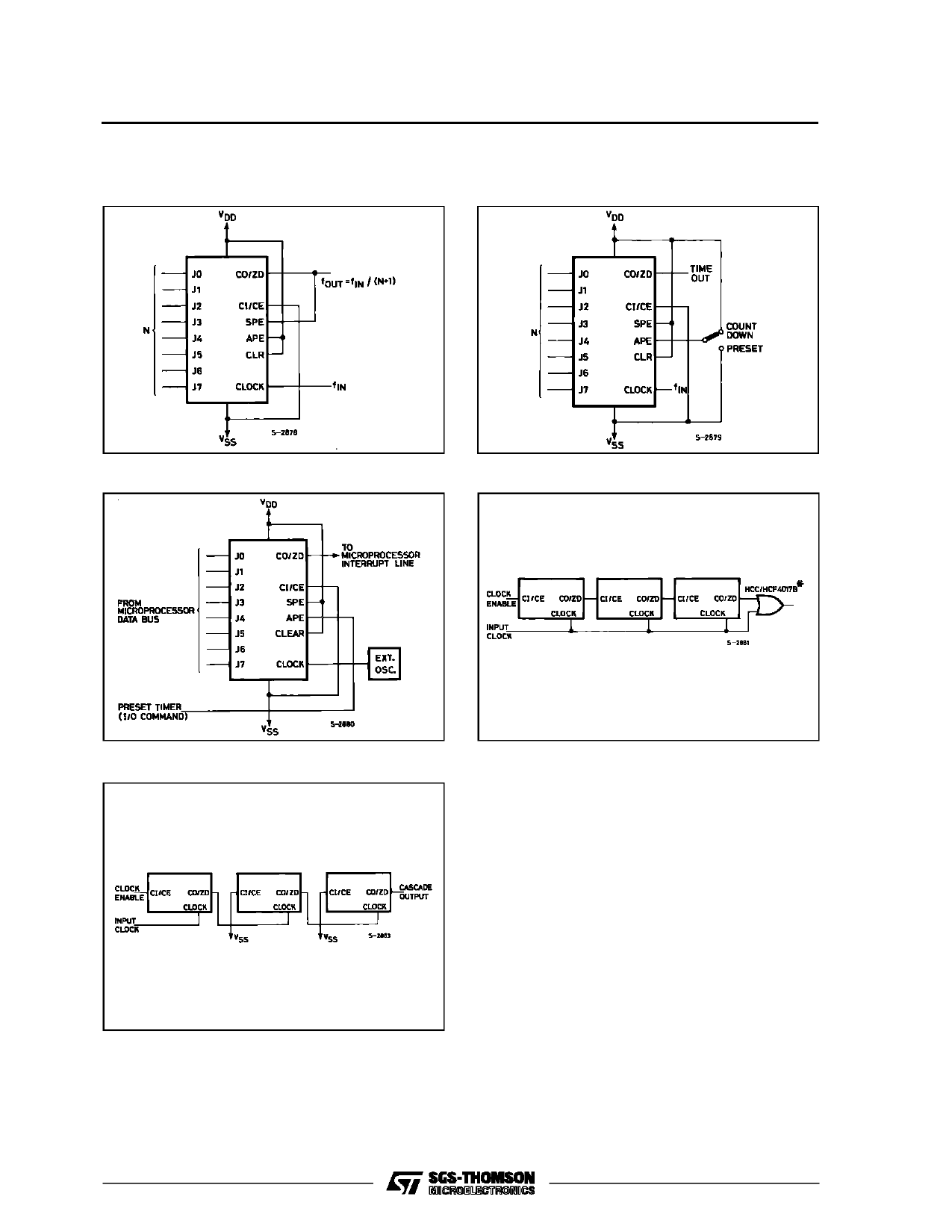

TYPICAL APPLICATIONS

Divide-by-”N” Counter.

Programmable Timer.

Microprocessor Interrupt Timer.

Synchronous Cascading.

Microprocessor Interrupt Timer.

* An output spike (160ns @ VDD = 5V) occurs whenever two or

more devices are cascaded in the parallel-clocked mode be-

cause the clock-to-carry out delay is greater than the carry-in-to-

carry out delay. This spike is eliminated by gating the out put

of the last device with the clock as shown.

8/13